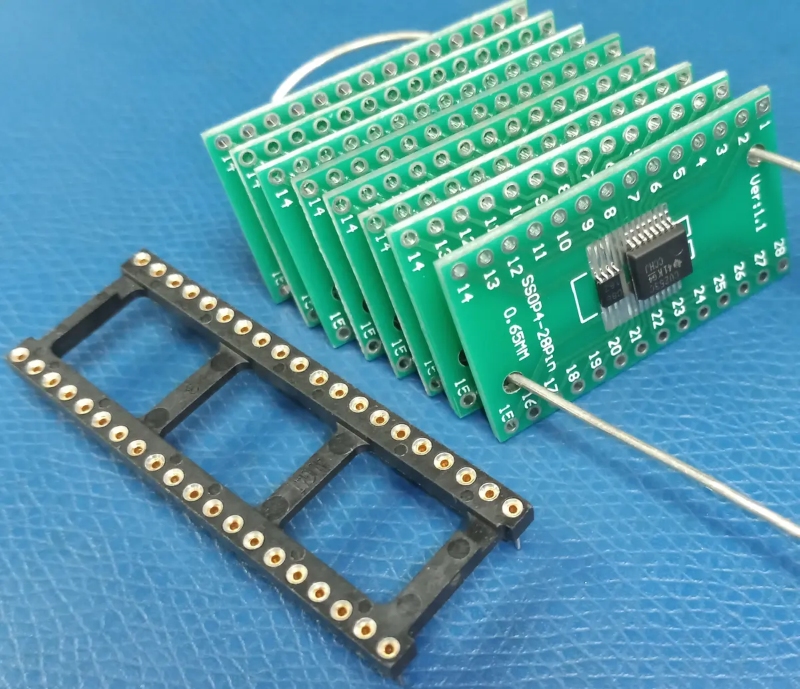

Photo shows a mix of SSOP and TSOP parts on the front.

For the moment, nothing but empty SOIC pads exist on back.

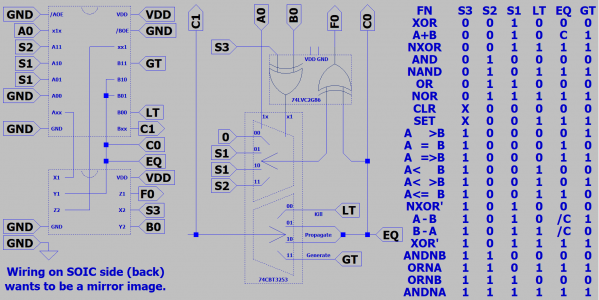

Individual slices need some wires between those SOIC pads.

Complete assembly might look like eight books on a DIP40 shelf.

A floppy pigtail might bring in power better than rely on DIP pins.

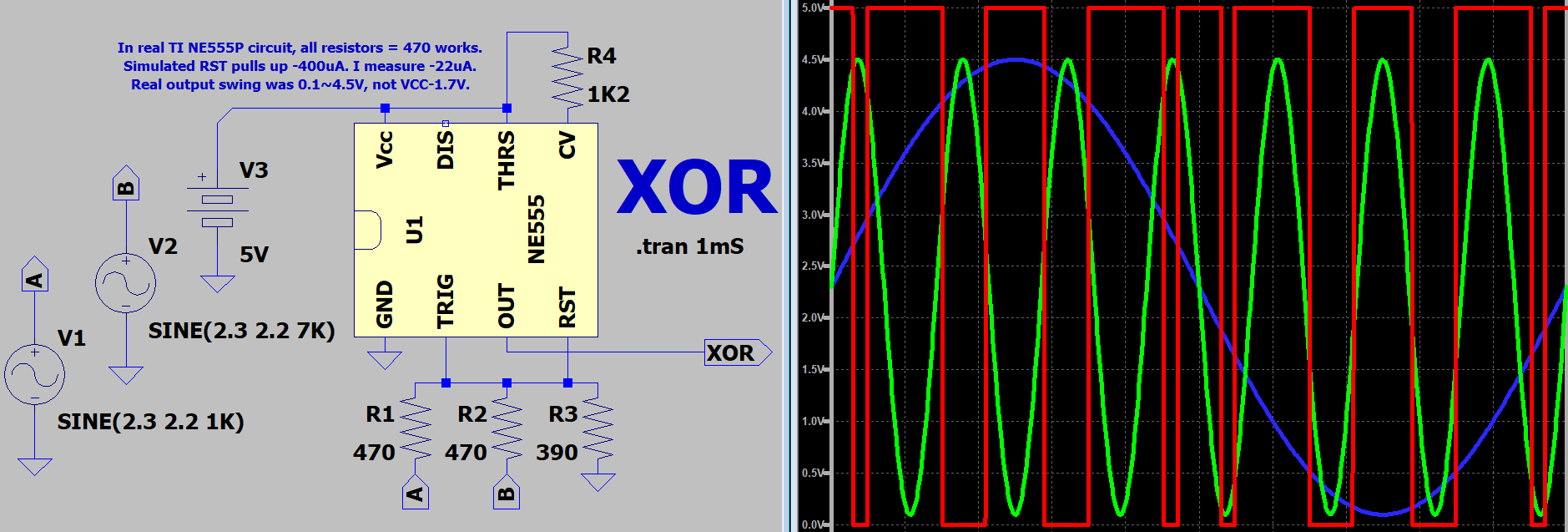

74LVC2G86 XOR gates load the chain about 5pF per slice.

74AUC2G86 XOR could reduce that to about 2.5pF per.

AUC would need a separate 2.7V rail or downregulator, can't

operate at same 5.5V as fastest voltage for CBT multiplexers.

I wonder if emitter followers could help buffer XOR inputs?

KSP10 claims less than 1pF. One base-emitter voltage drop

should be no problem for driving AUC logic's 0.8V threshold.

Even if it slows those final XORs, it might speed up the chain.

I say KSP10 cause I own a bag of 1000 or maybe it was 5000.

Maybe Schottky diodes were the 5000, something was 5000.

Arrow was closing out for under a penny, so why the hell not?

Some kinda gold doped RF transistor that refuses to saturate.

https://www.mouser.com/datasheet/2/149/KSP10-889509.pdf

Left myself no room on these slices to be thinking of buffers.

Where am I supposed to put those? Build as-is and measure.

Maybe there is no problem except I keep changing the plan.

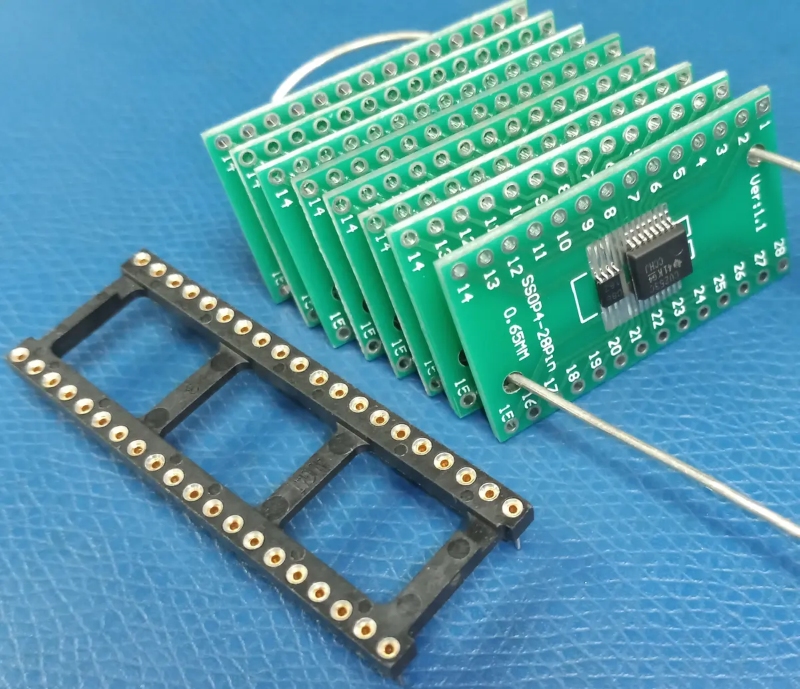

For the moment, nothing but empty SOIC pads exist on back.

Individual slices need some wires between those SOIC pads.

Complete assembly might look like eight books on a DIP40 shelf.

A floppy pigtail might bring in power better than rely on DIP pins.

74LVC2G86 XOR gates load the chain about 5pF per slice.

74AUC2G86 XOR could reduce that to about 2.5pF per.

AUC would need a separate 2.7V rail or downregulator, can't

operate at same 5.5V as fastest voltage for CBT multiplexers.

I wonder if emitter followers could help buffer XOR inputs?

KSP10 claims less than 1pF. One base-emitter voltage drop

should be no problem for driving AUC logic's 0.8V threshold.

Even if it slows those final XORs, it might speed up the chain.

I say KSP10 cause I own a bag of 1000 or maybe it was 5000.

Maybe Schottky diodes were the 5000, something was 5000.

Arrow was closing out for under a penny, so why the hell not?

Some kinda gold doped RF transistor that refuses to saturate.

https://www.mouser.com/datasheet/2/149/KSP10-889509.pdf

Left myself no room on these slices to be thinking of buffers.

Where am I supposed to put those? Build as-is and measure.

Maybe there is no problem except I keep changing the plan.

Last edited:

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)