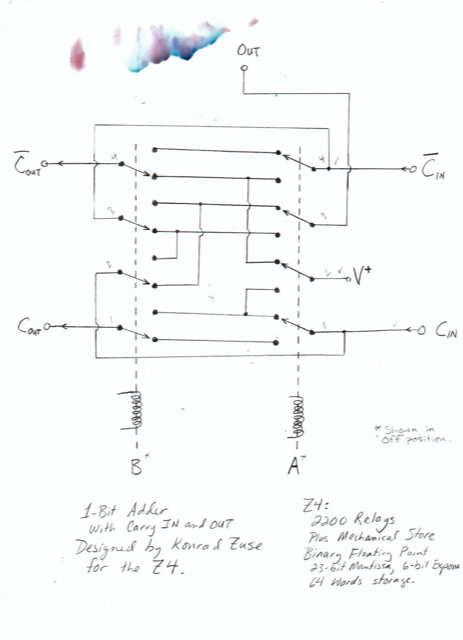

While composing a difficult email to Japan, fishing long lost secrets of Takahasi's non-quantum DGate:

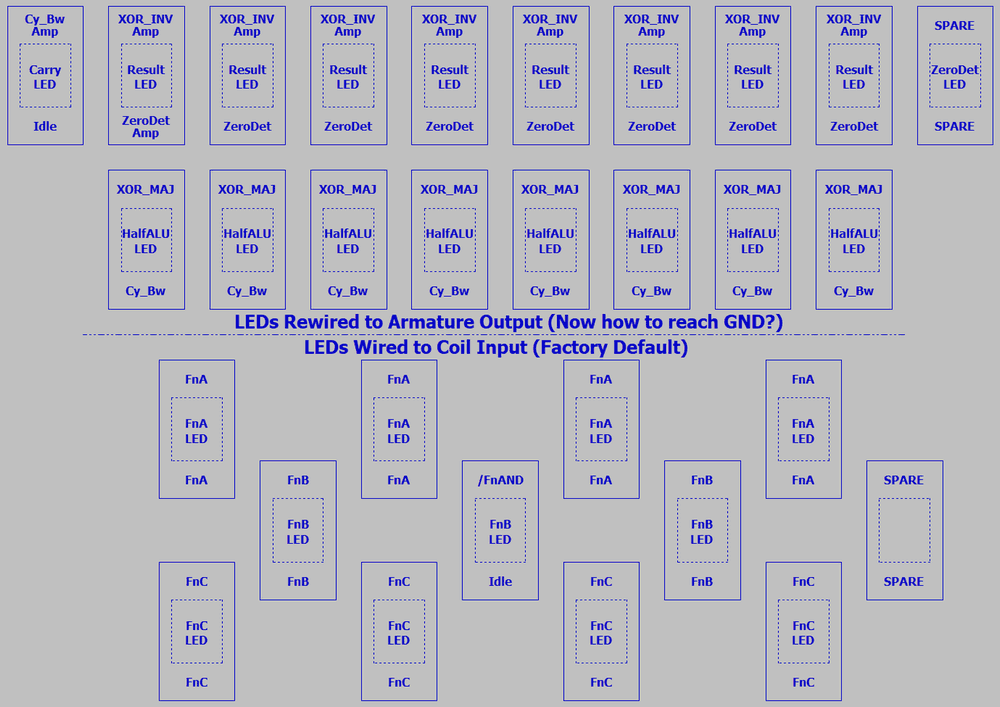

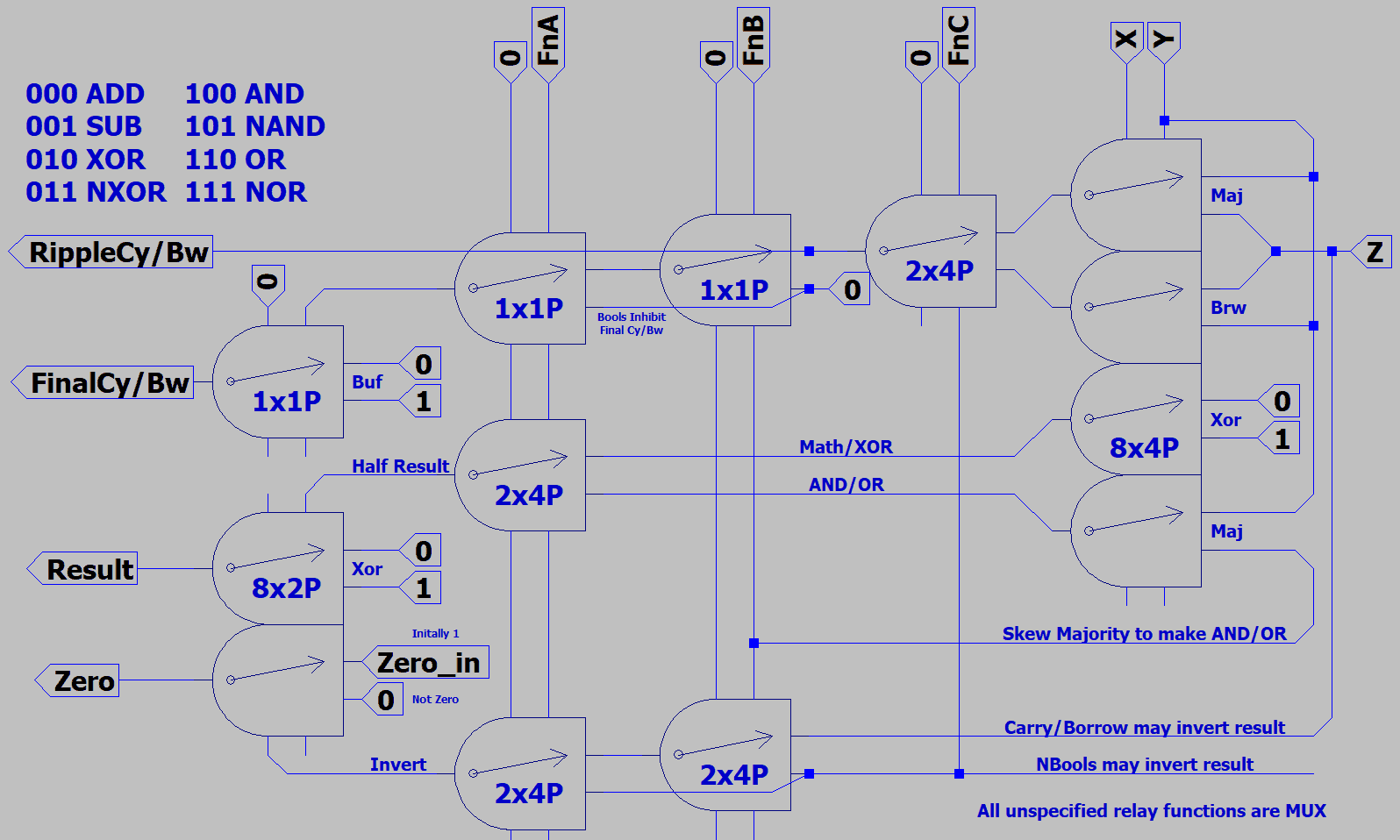

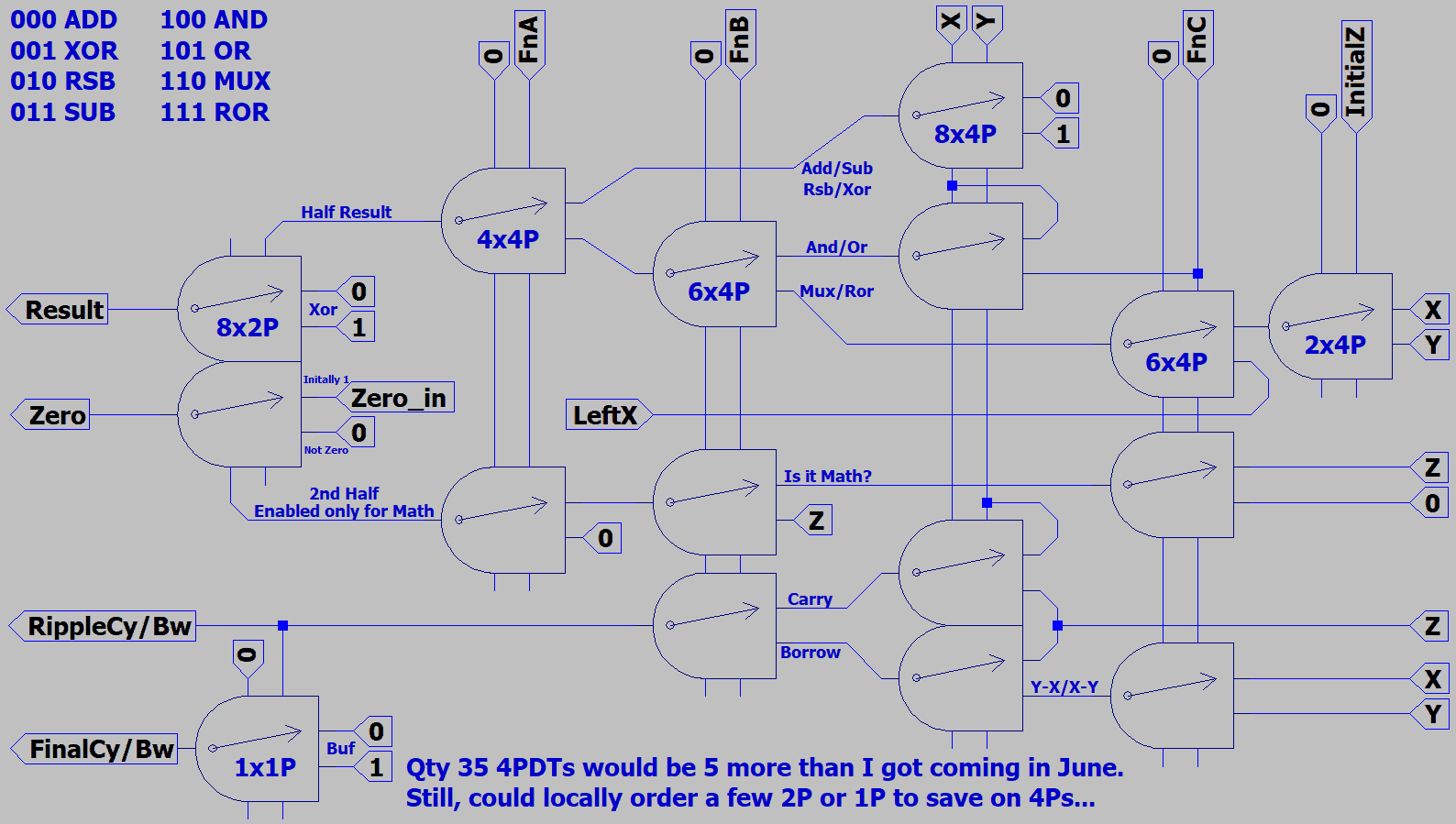

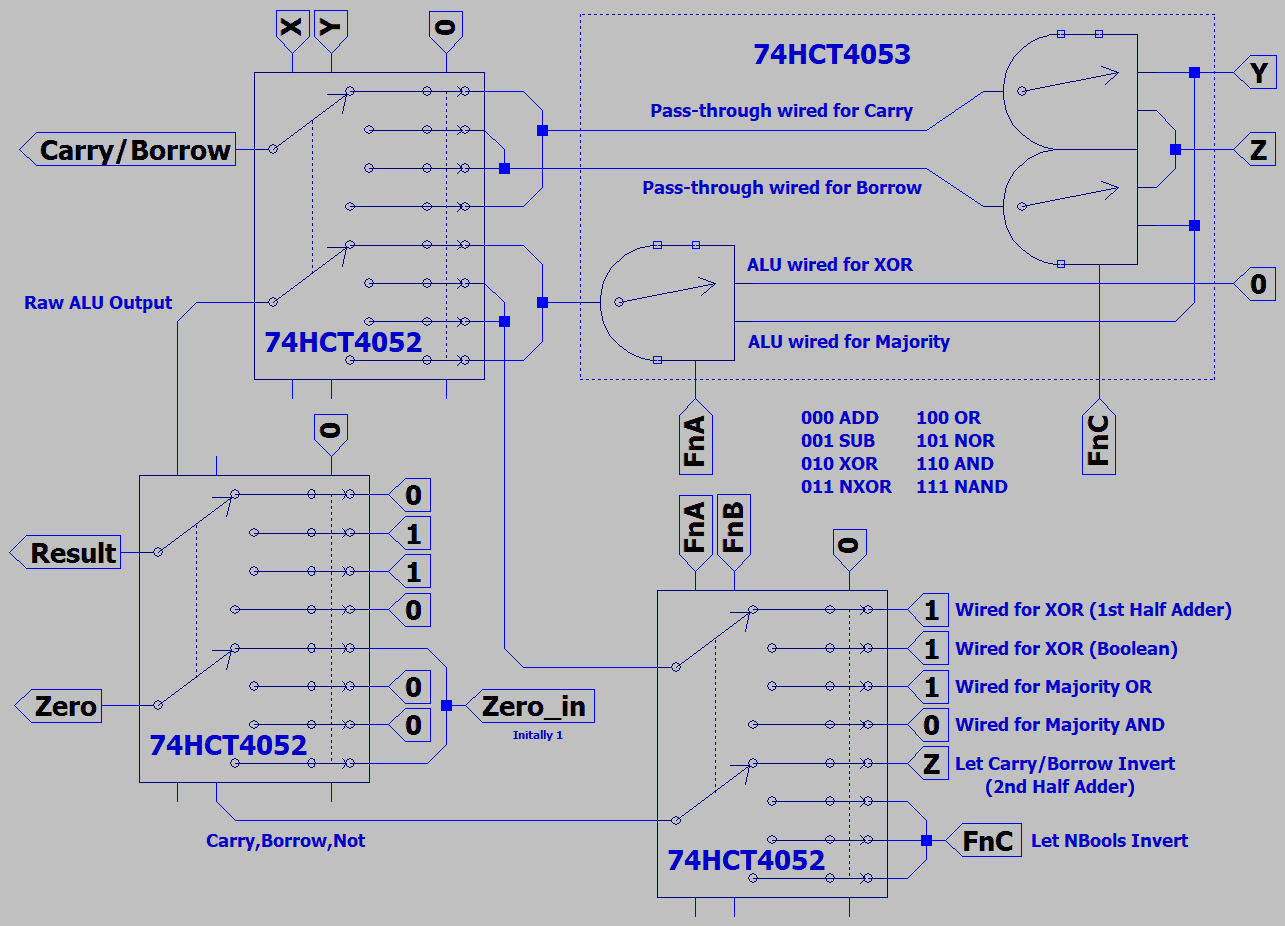

I was drawing lame pictures again to make up for my complete illiteracy in both Japango and Engrish.

But none of that is my current point, only the story of how I've gone from confused to completely nuts...

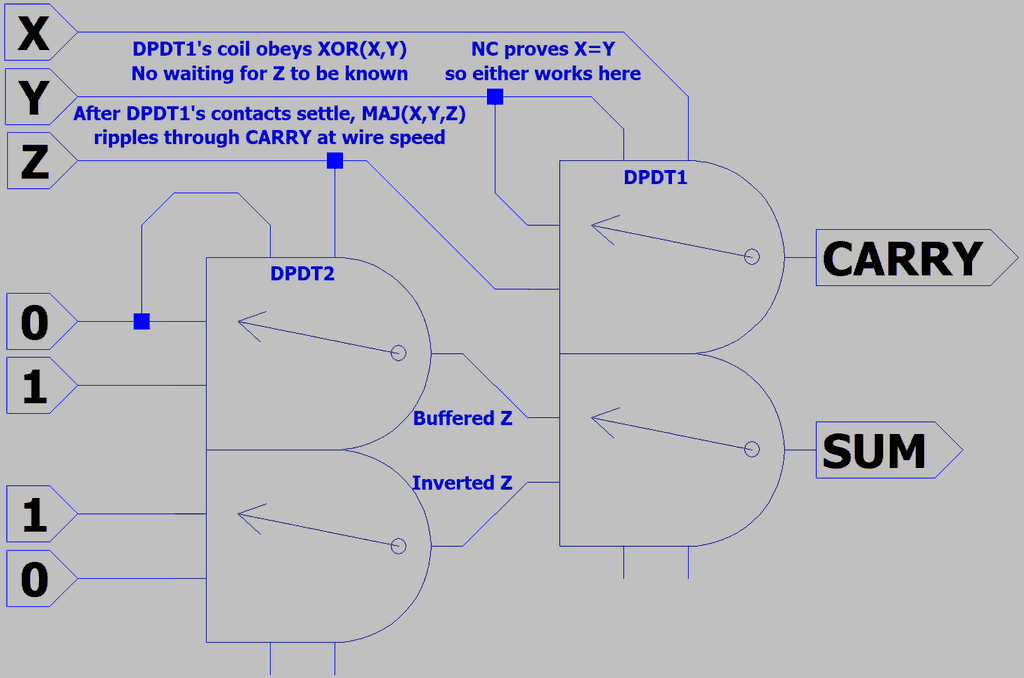

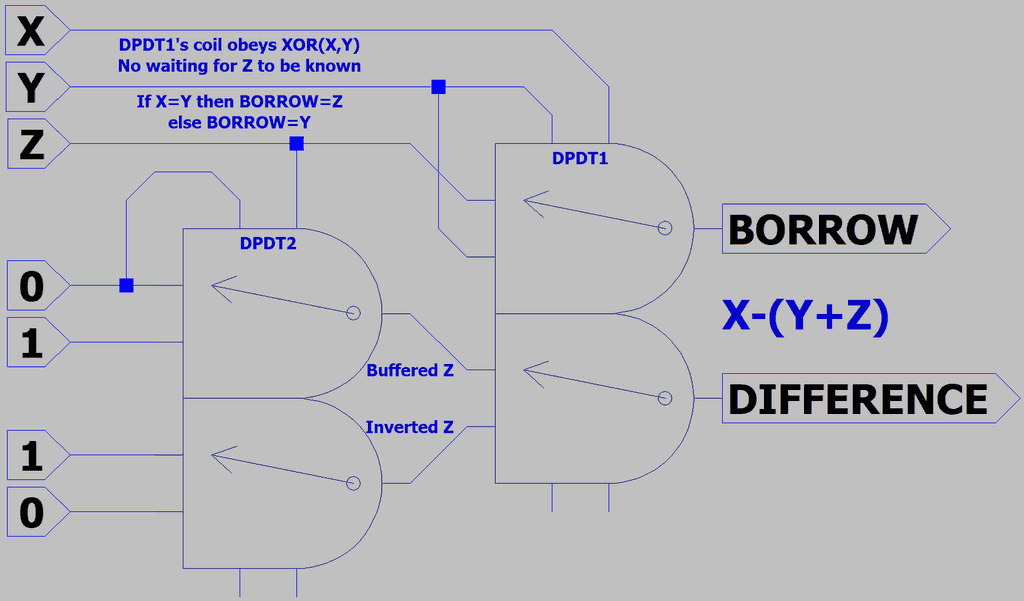

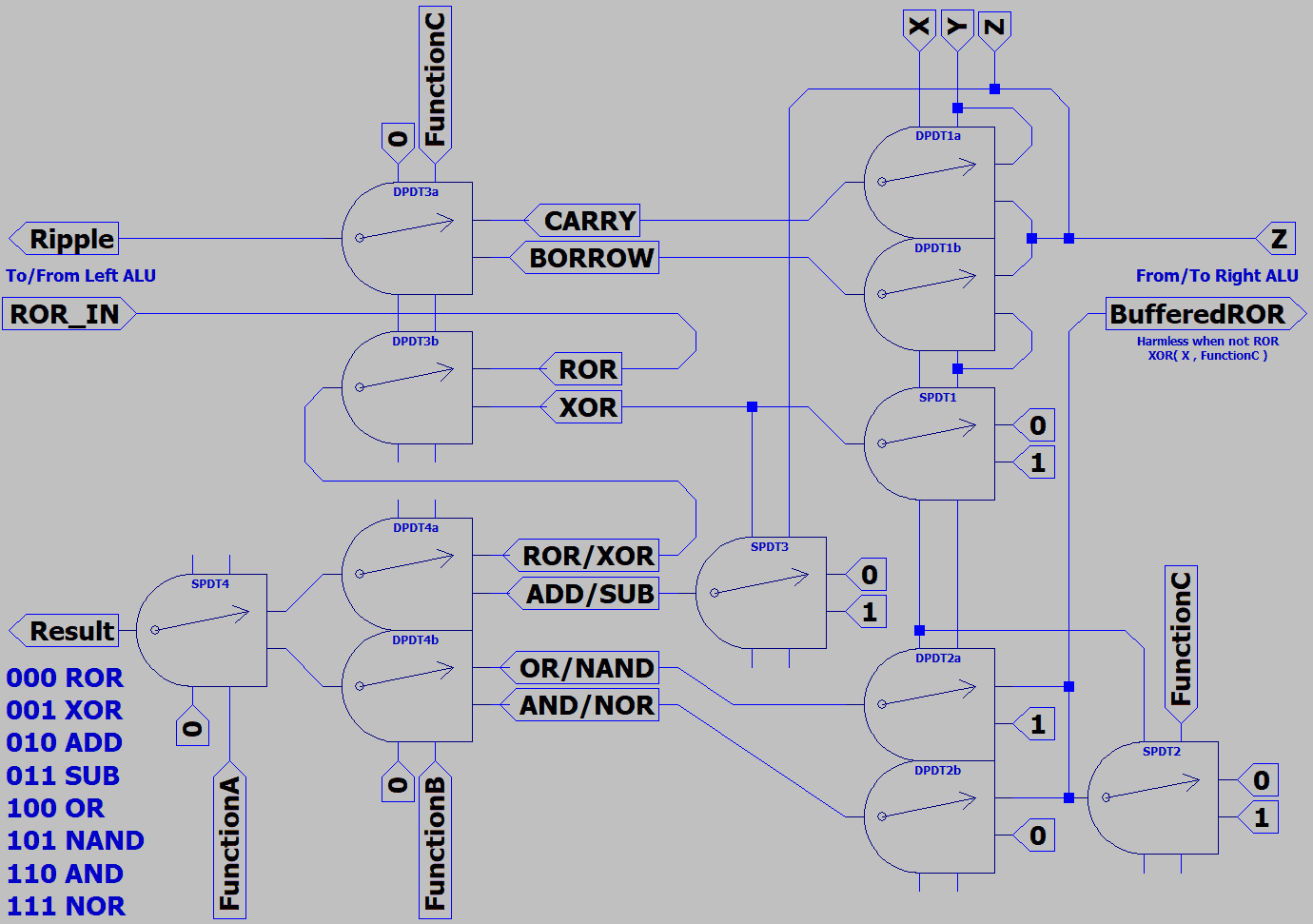

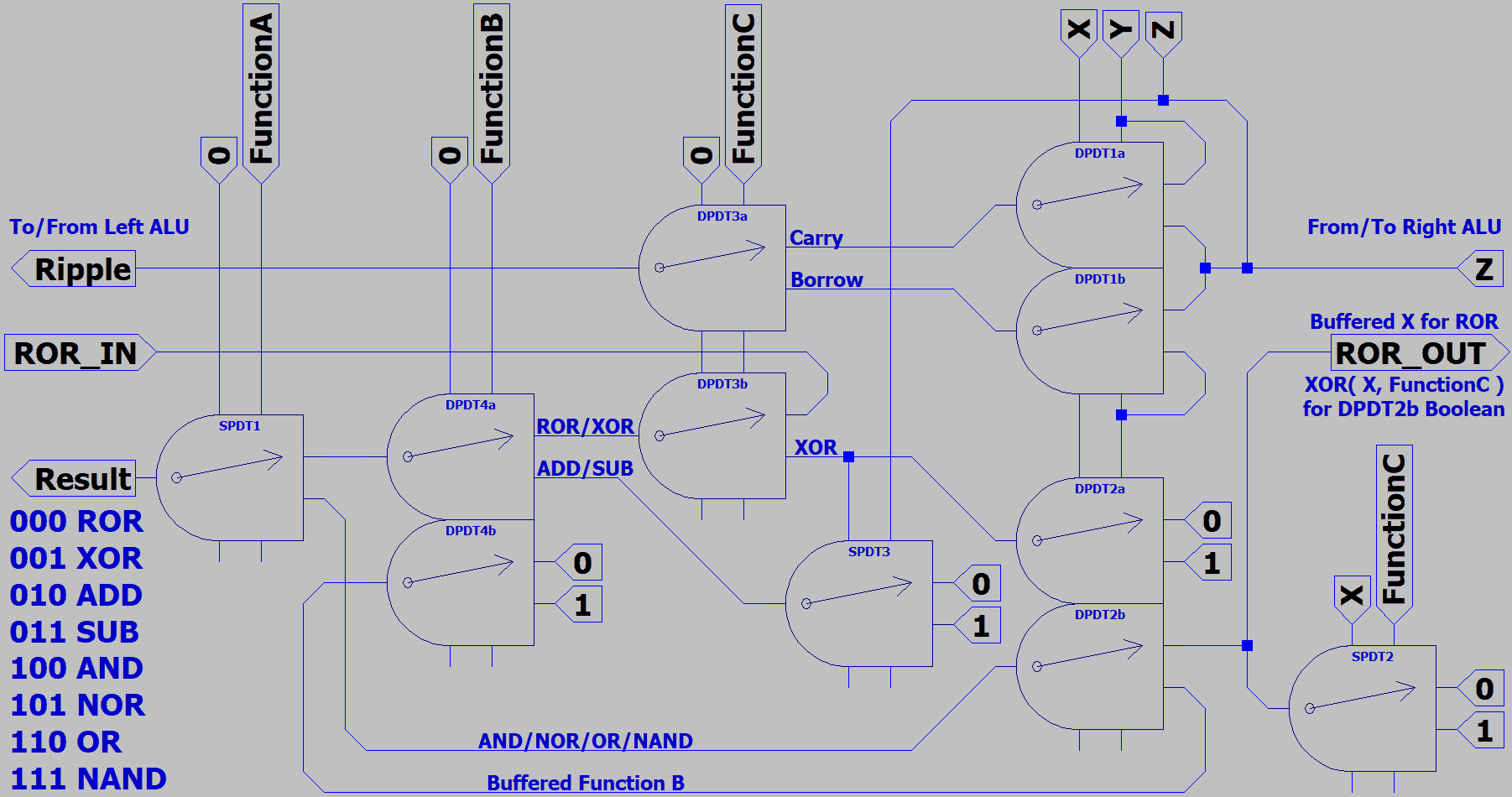

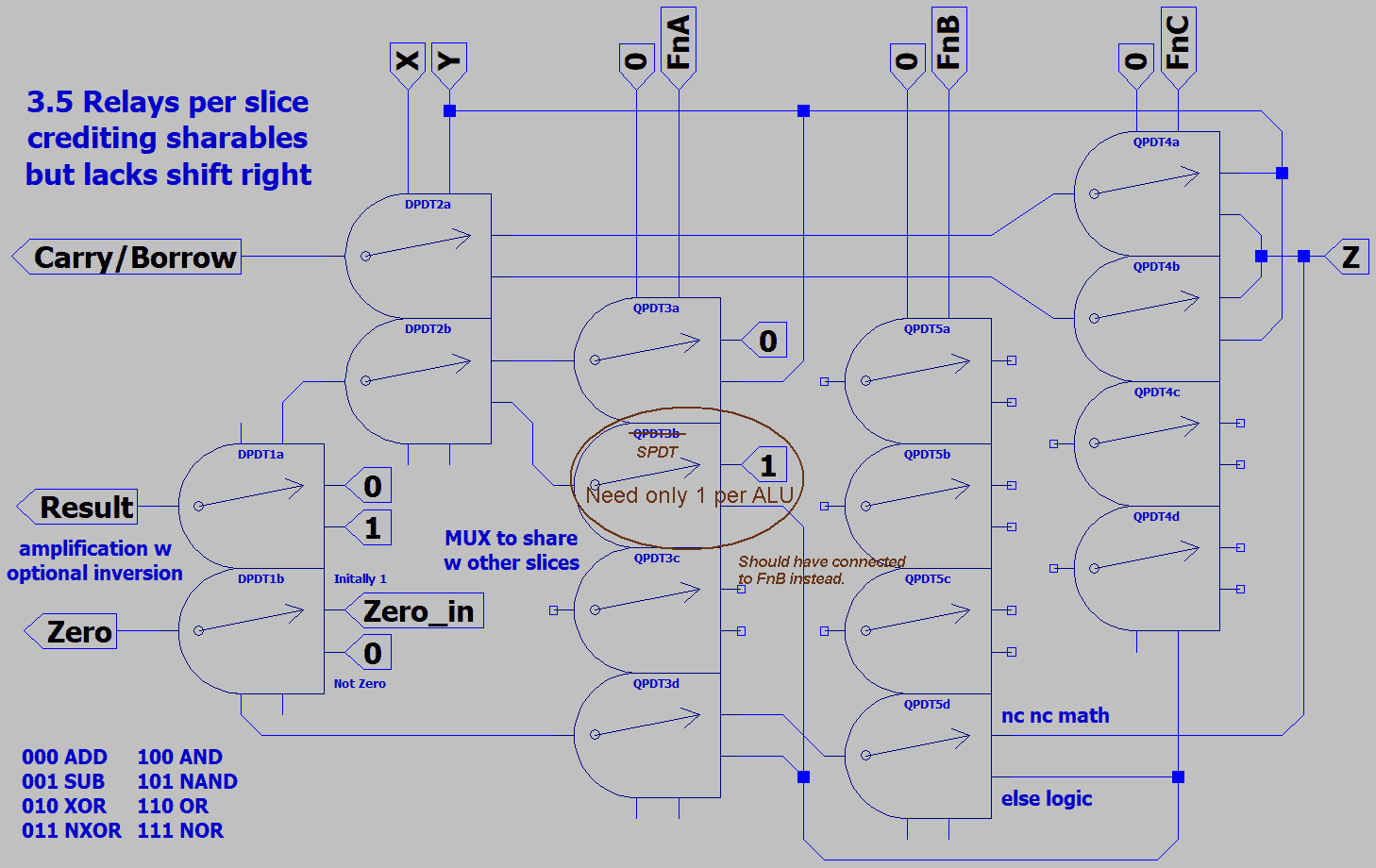

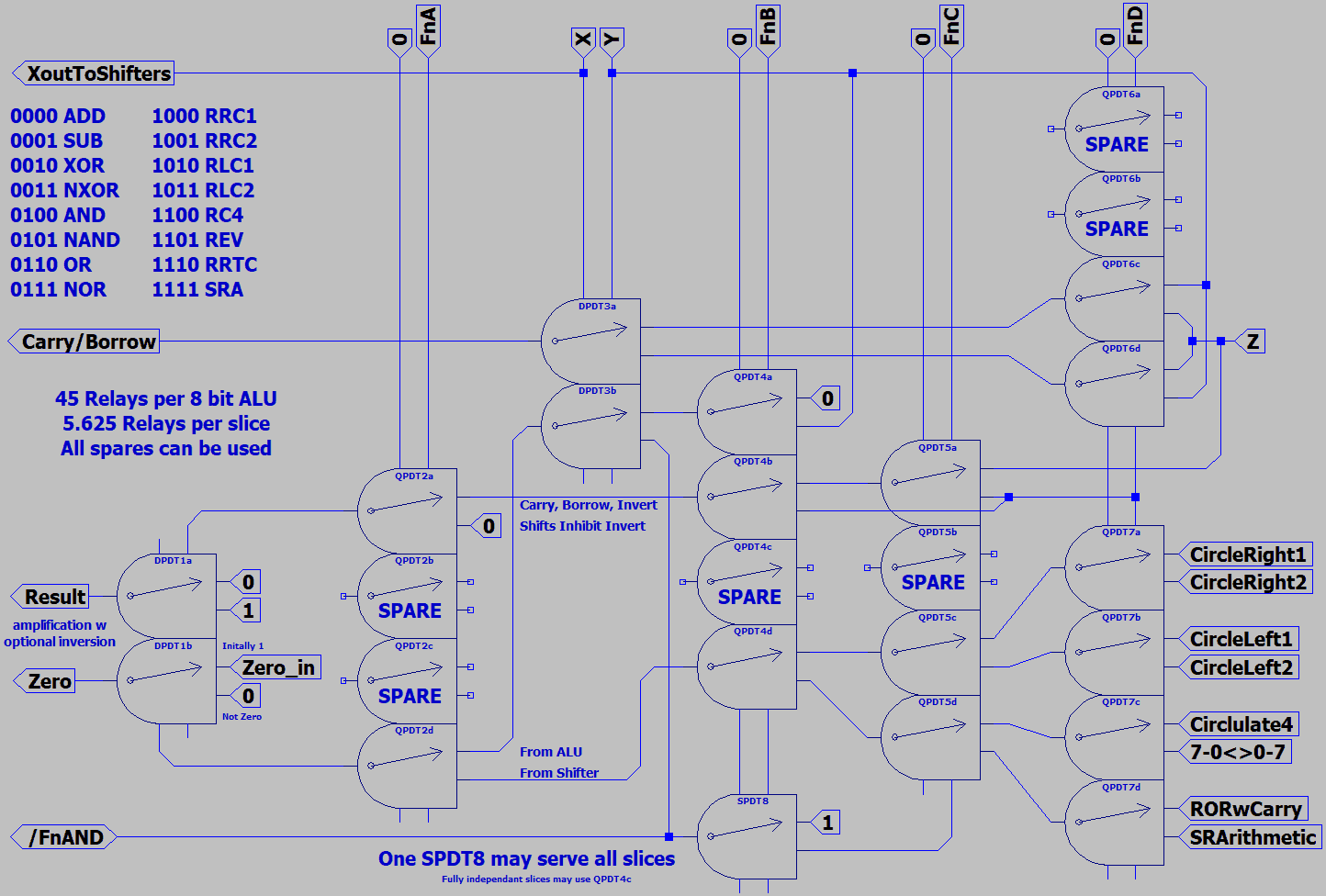

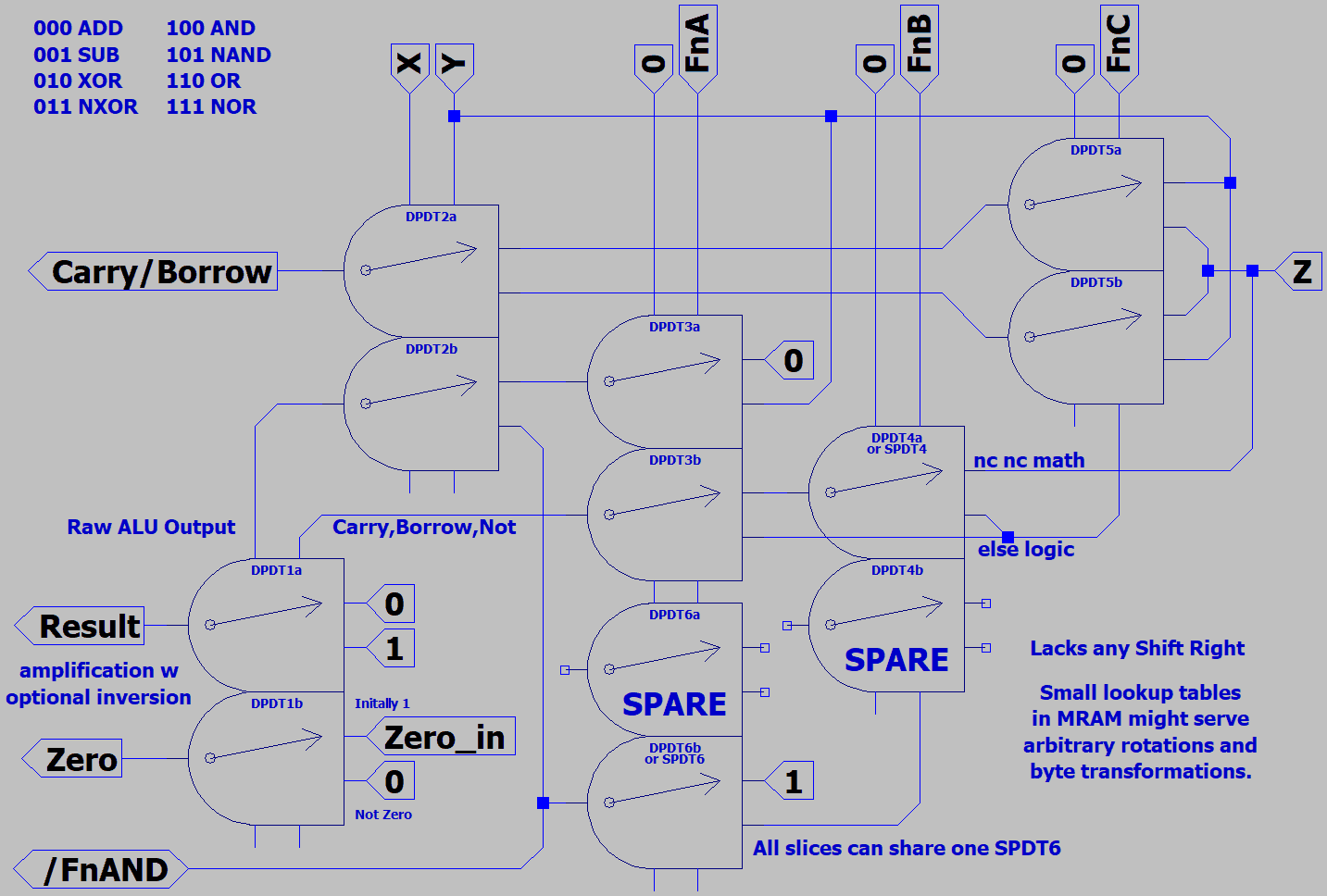

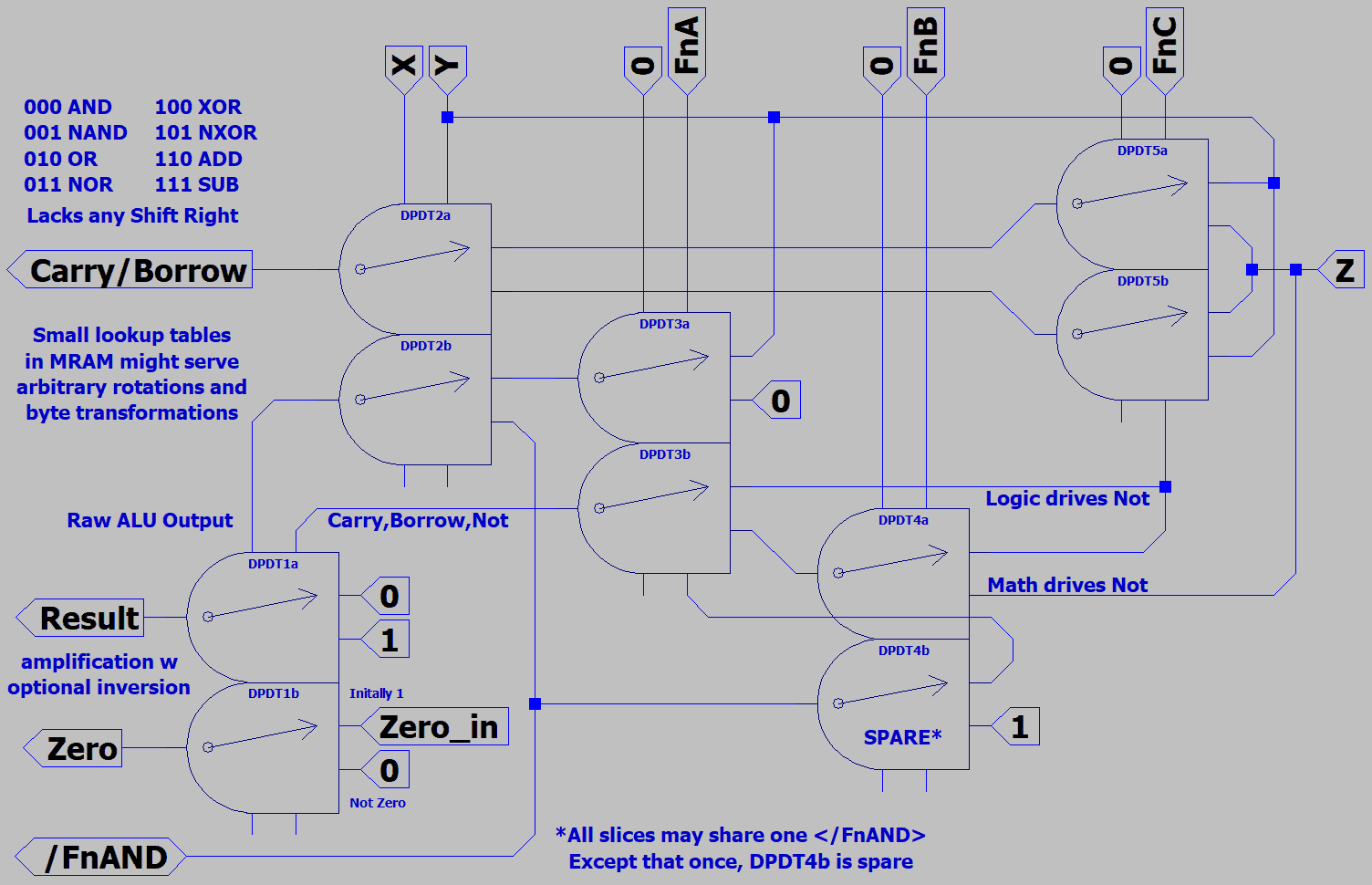

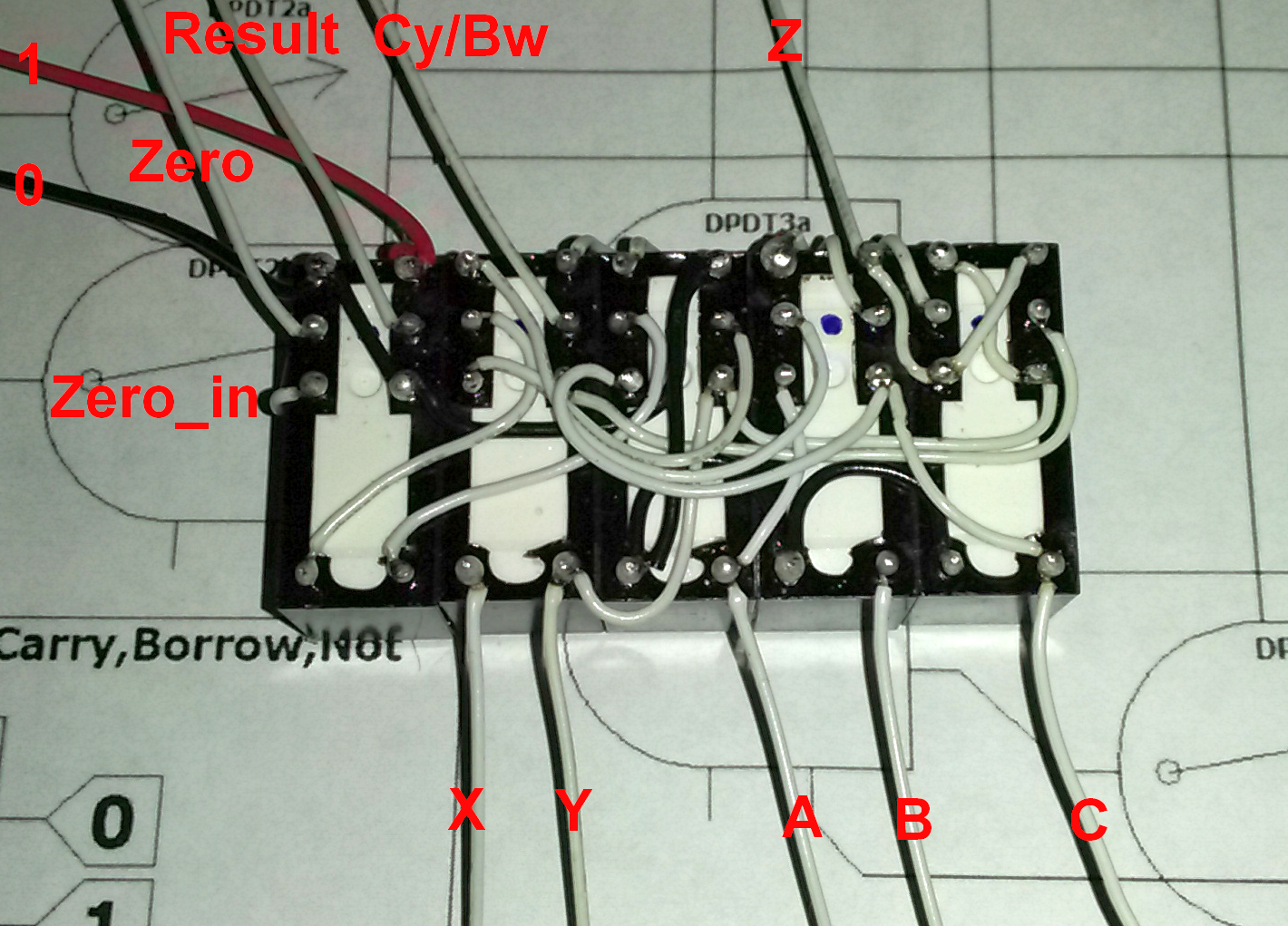

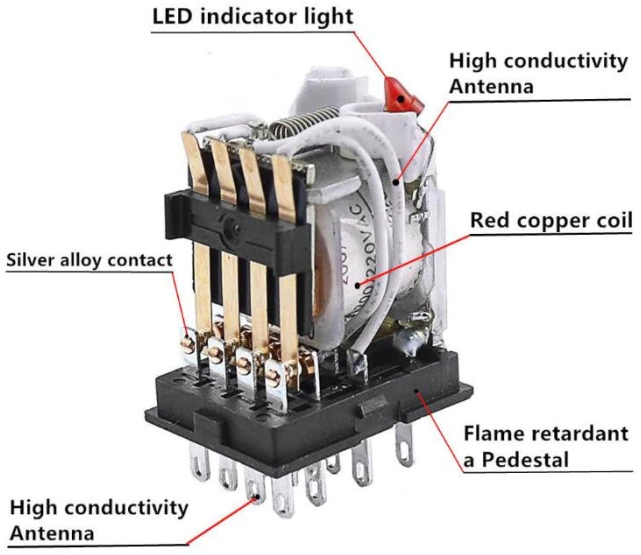

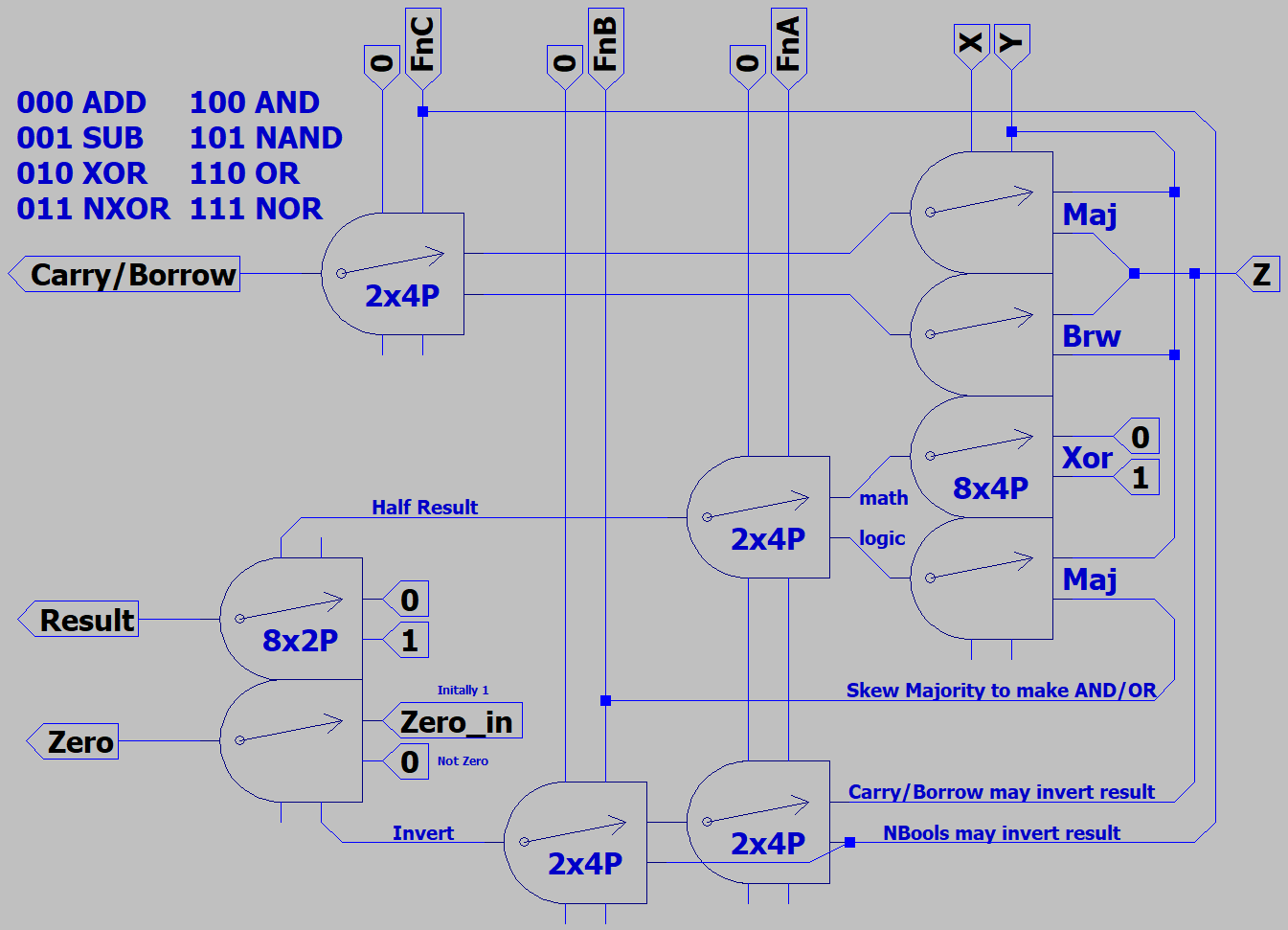

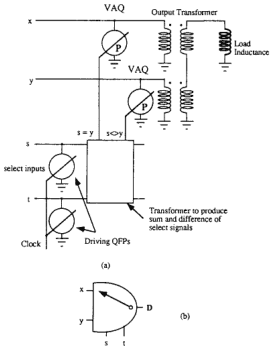

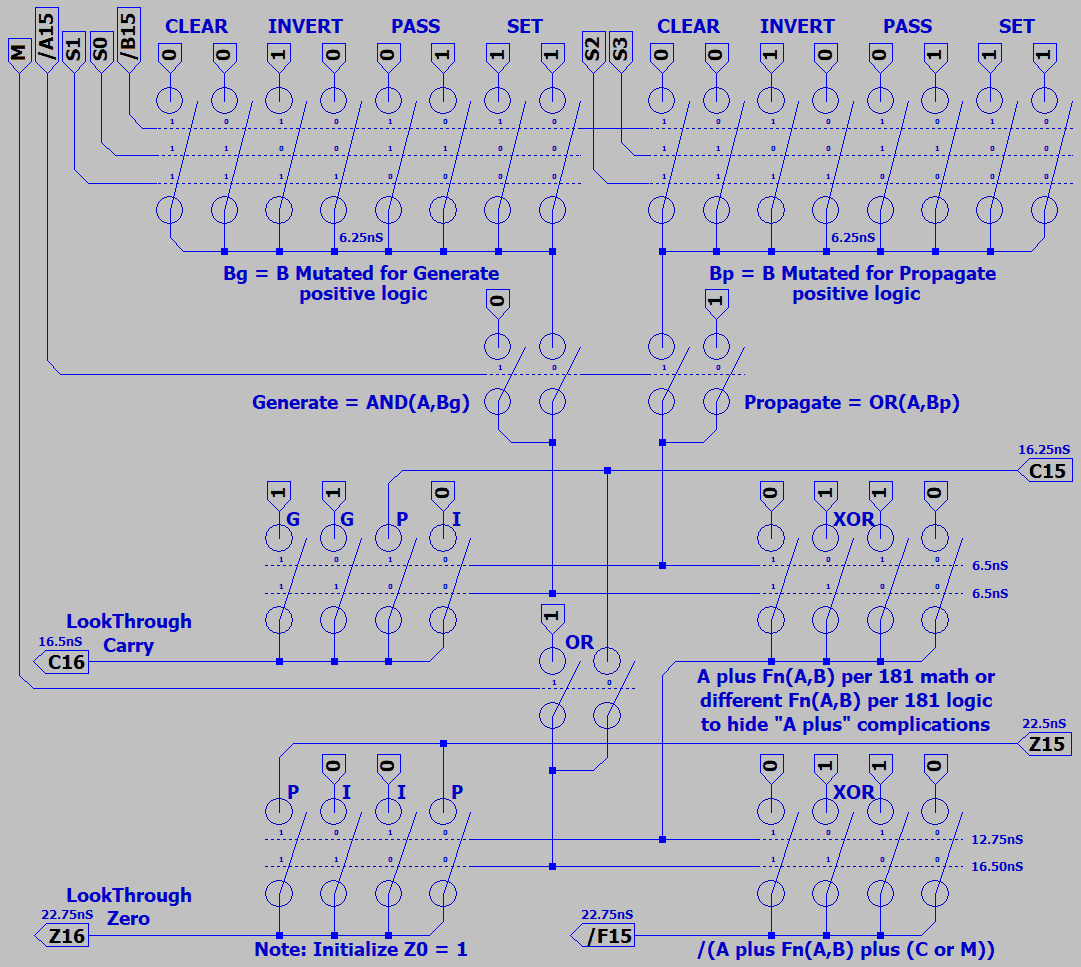

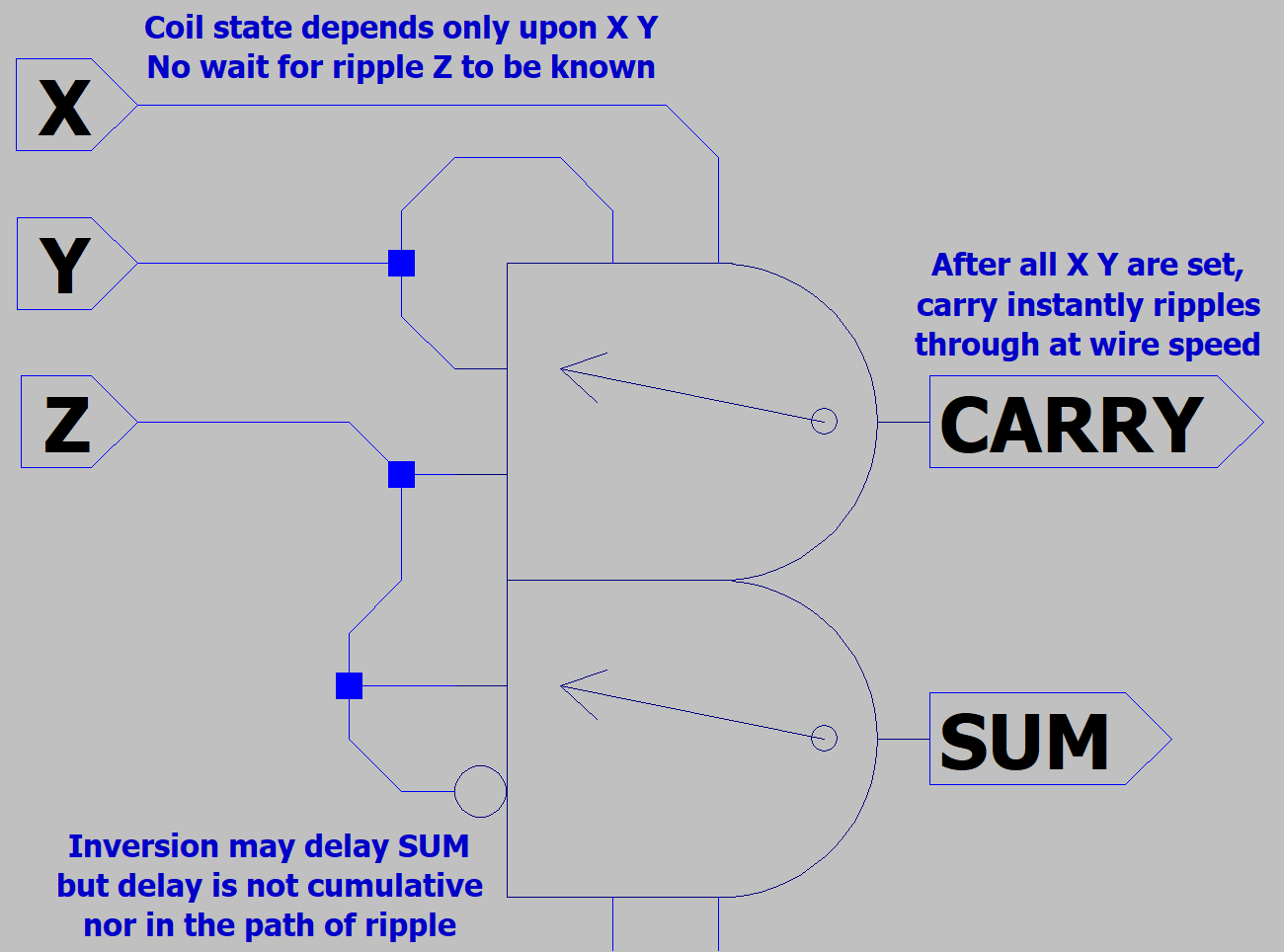

I stumbled upon something that only relays (and maybe mosfets) can do. Instant Pass Through Carry.

Check it out: The coil performs XOR, and nothing thereafter needs to move for Carry to ripple through.

Once all carries are known. Wait one invert of delay, and all sums can also be known. The number of

bits doesn't matter. Carry look-ahead in this case would be pointless, ripple may be as quick or better.

If you are hurried for SUMs and don't want to wait one extra cycle on relay inversion.

You could use inverting transformers instead. No moving parts, and the speed of wire.

Transformers can't invert DC. If you chose to use transformers, would have to rely on

opposing AC phases. Two signals of similar phase won't activate, but opposites would.

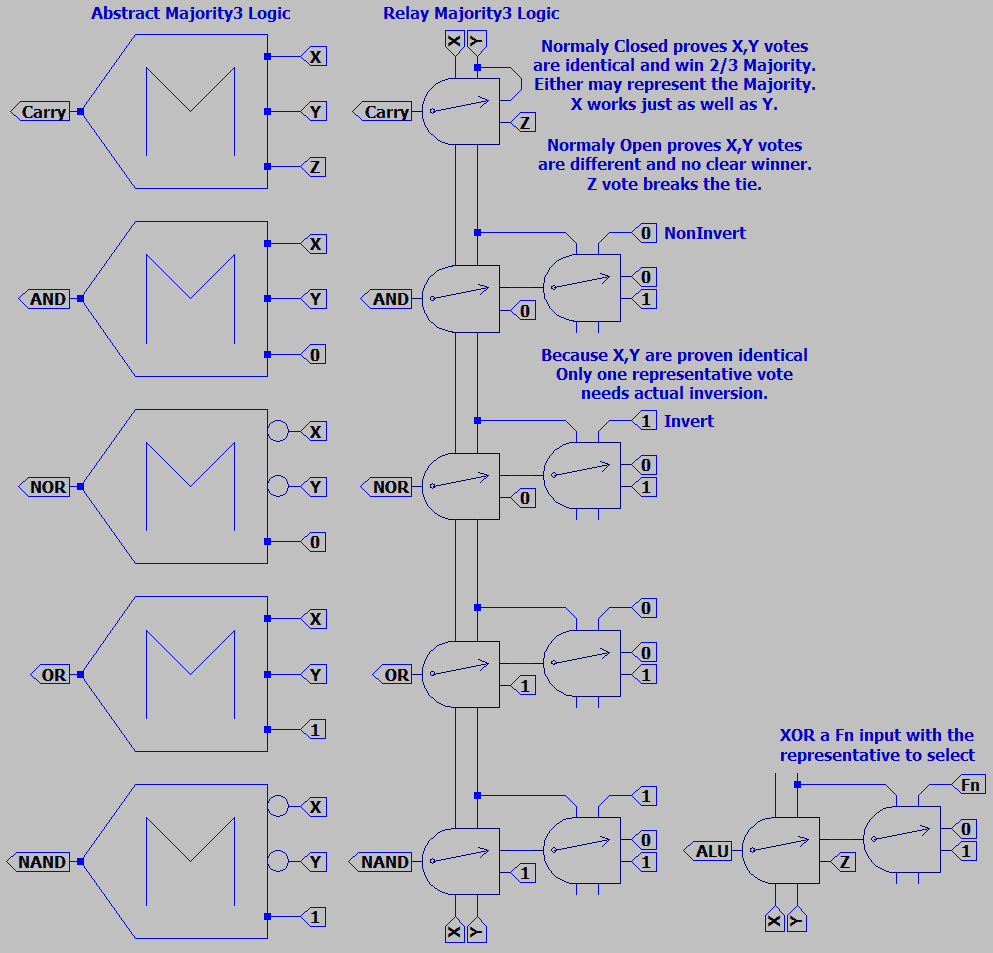

Wether AC or DC driven, a relay's coil is activated by the same logic function as XOR.

Doesn't matter which end of a XOR coil might also feed the normally closed contact.

Normally closed proves both coil inputs to be in the same AC or DC state anyhow.

If X Y are the same, they also rule the Majority. If X Y differed, the switch would be

pointing at Z instead, for a tie breaker. Carry shares the same logic as Majority Vote.

I was drawing lame pictures again to make up for my complete illiteracy in both Japango and Engrish.

But none of that is my current point, only the story of how I've gone from confused to completely nuts...

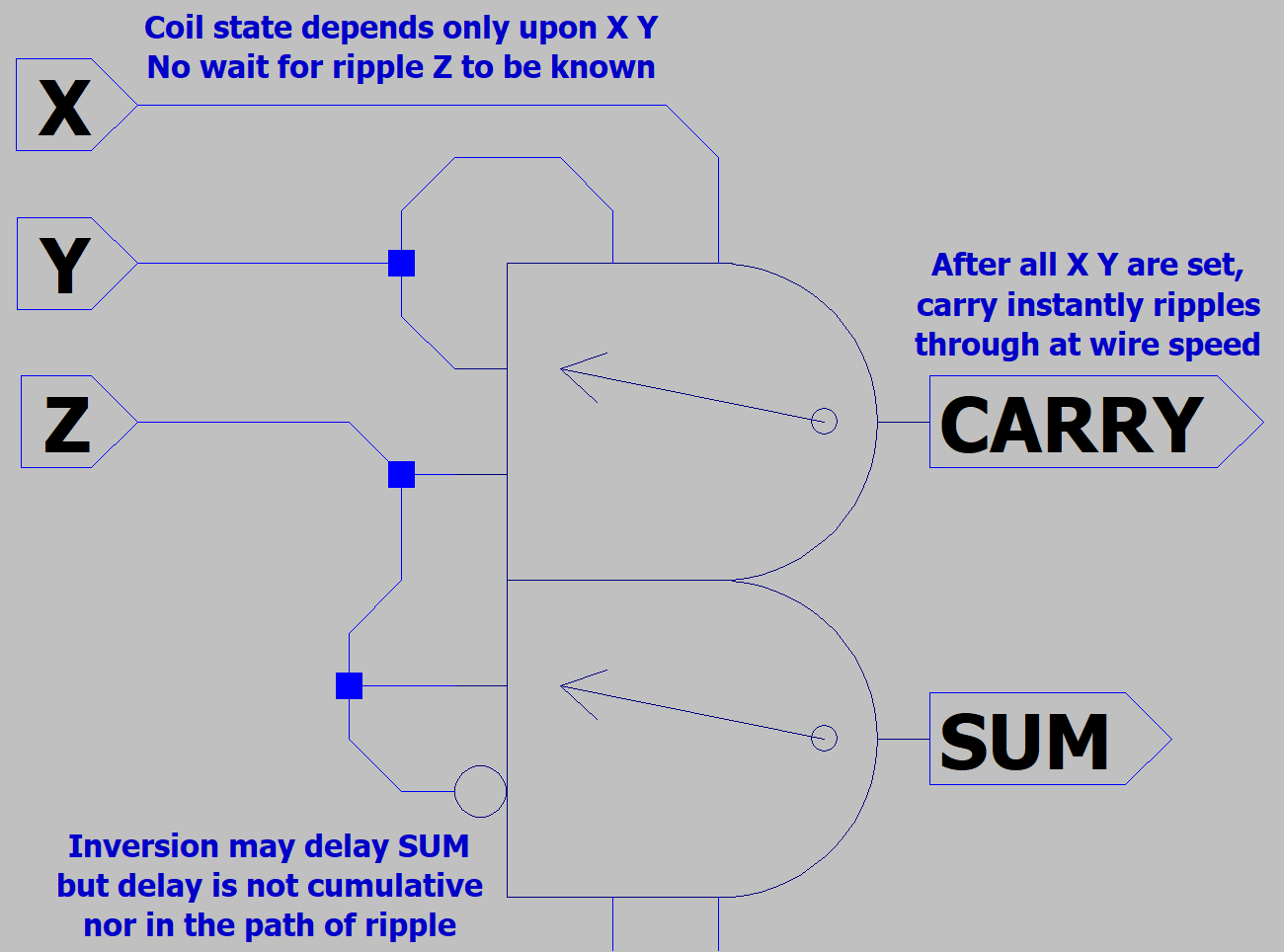

I stumbled upon something that only relays (and maybe mosfets) can do. Instant Pass Through Carry.

Check it out: The coil performs XOR, and nothing thereafter needs to move for Carry to ripple through.

Once all carries are known. Wait one invert of delay, and all sums can also be known. The number of

bits doesn't matter. Carry look-ahead in this case would be pointless, ripple may be as quick or better.

If you are hurried for SUMs and don't want to wait one extra cycle on relay inversion.

You could use inverting transformers instead. No moving parts, and the speed of wire.

Transformers can't invert DC. If you chose to use transformers, would have to rely on

opposing AC phases. Two signals of similar phase won't activate, but opposites would.

Wether AC or DC driven, a relay's coil is activated by the same logic function as XOR.

Doesn't matter which end of a XOR coil might also feed the normally closed contact.

Normally closed proves both coil inputs to be in the same AC or DC state anyhow.

If X Y are the same, they also rule the Majority. If X Y differed, the switch would be

pointing at Z instead, for a tie breaker. Carry shares the same logic as Majority Vote.

Last edited:

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)