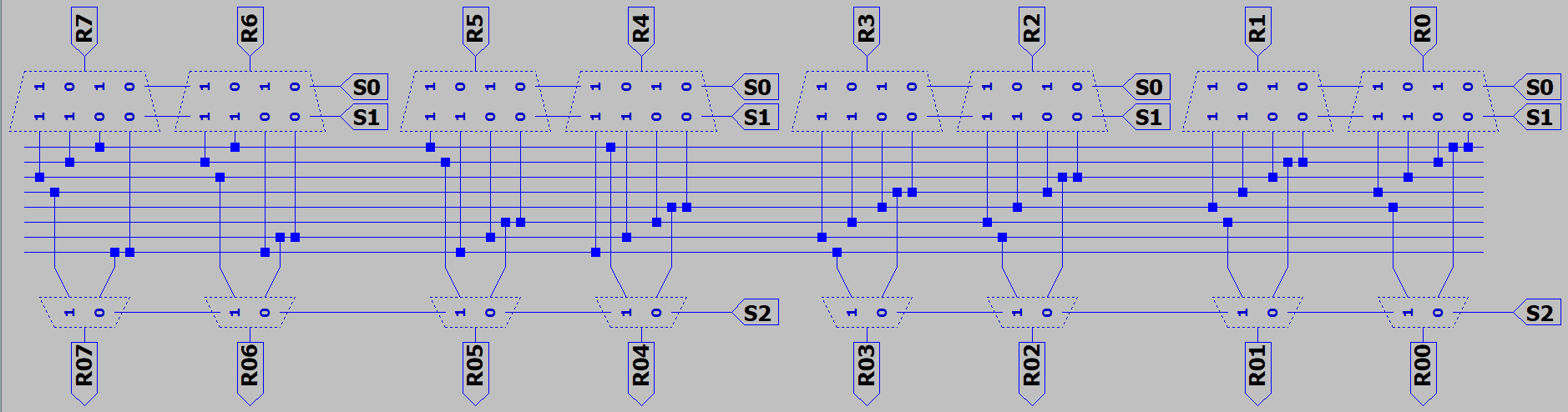

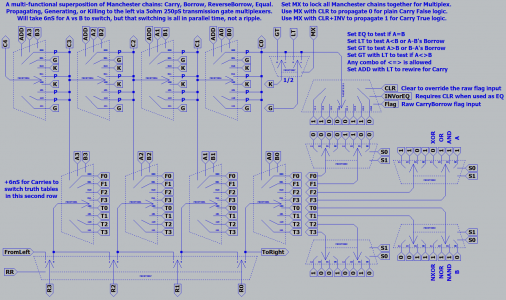

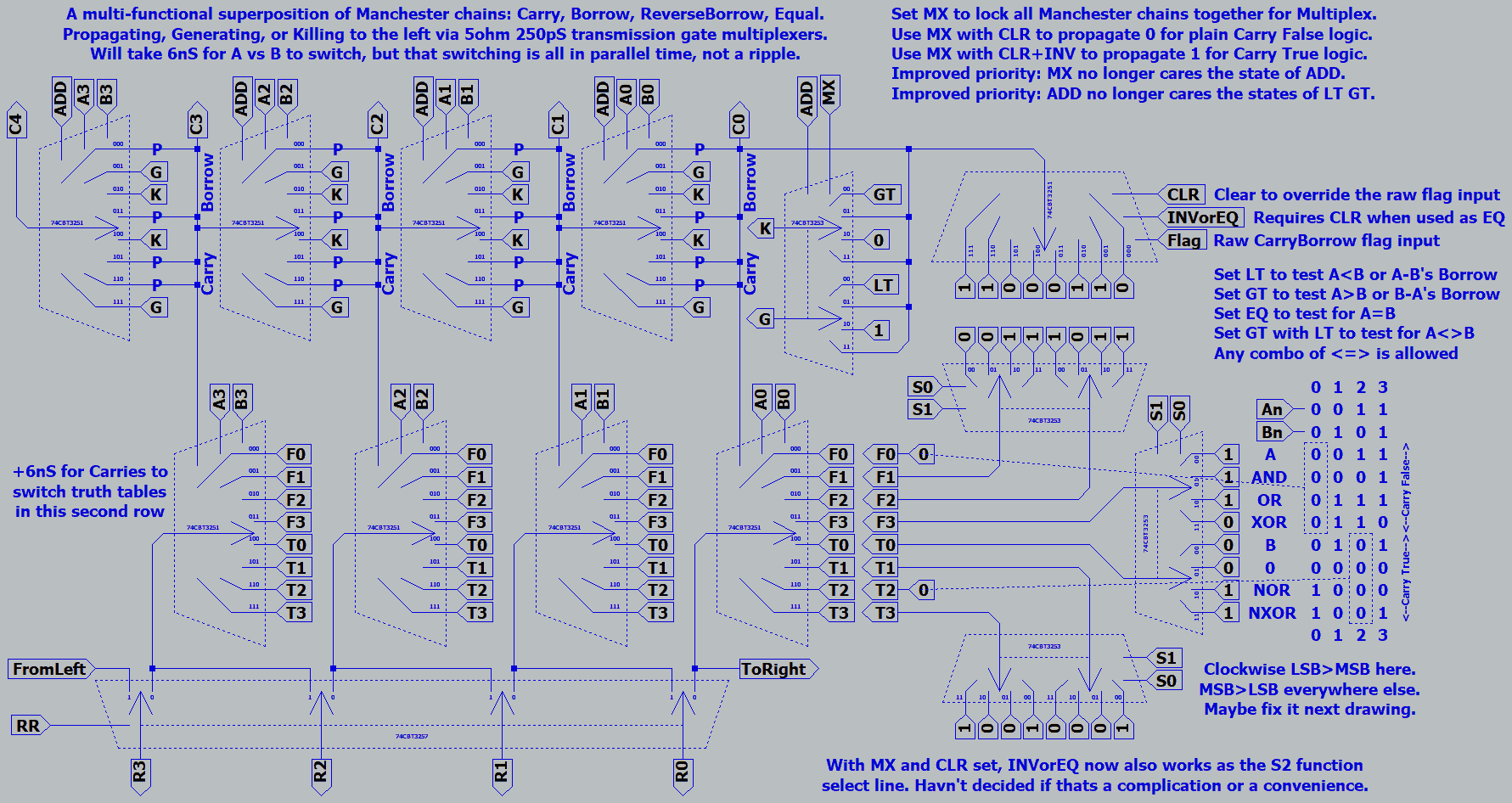

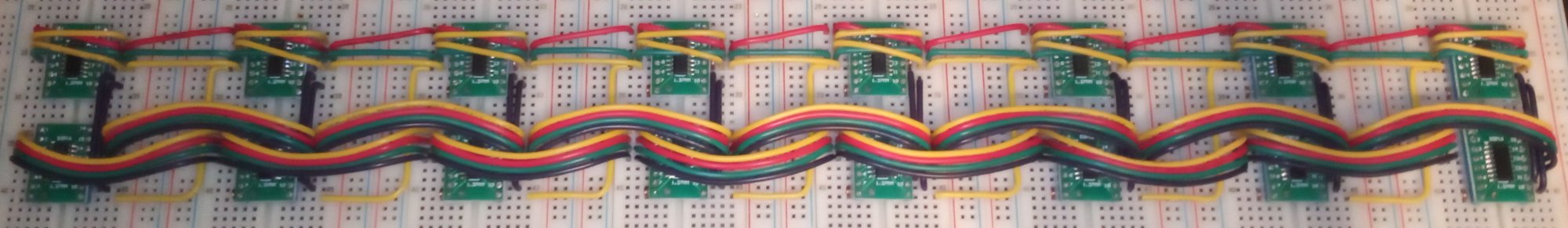

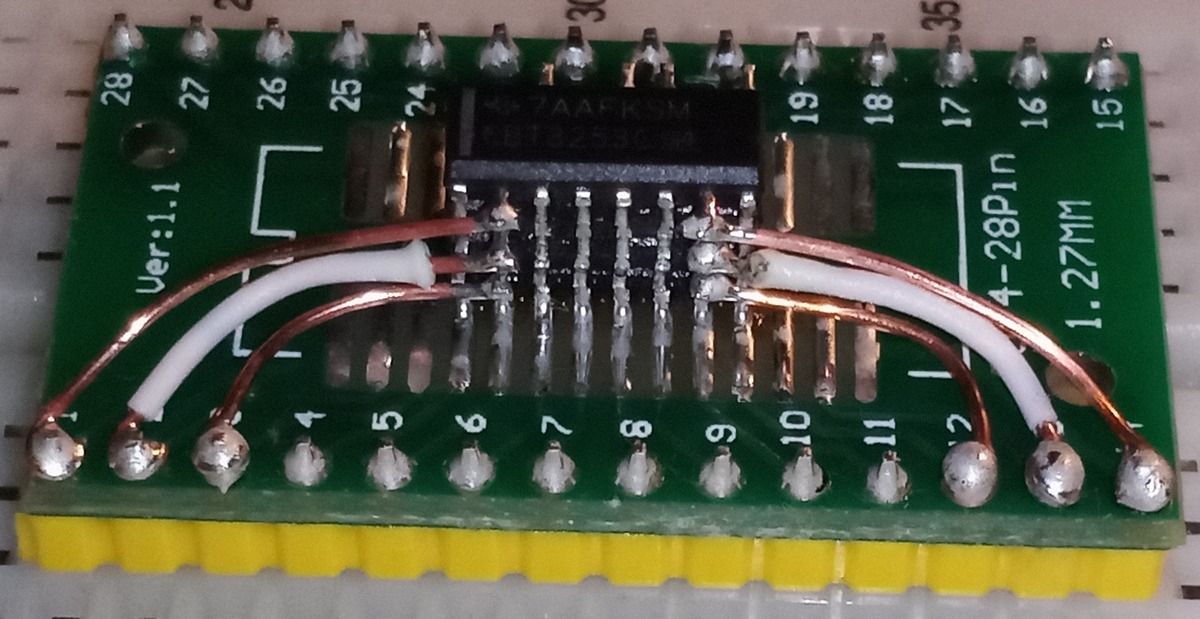

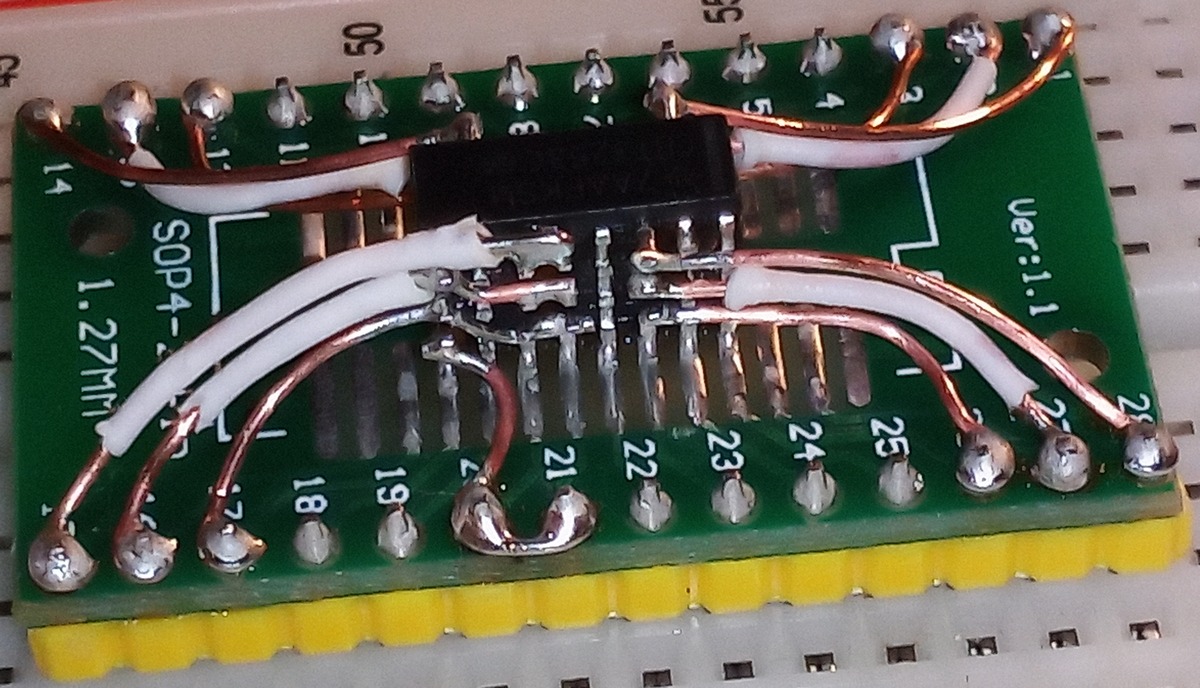

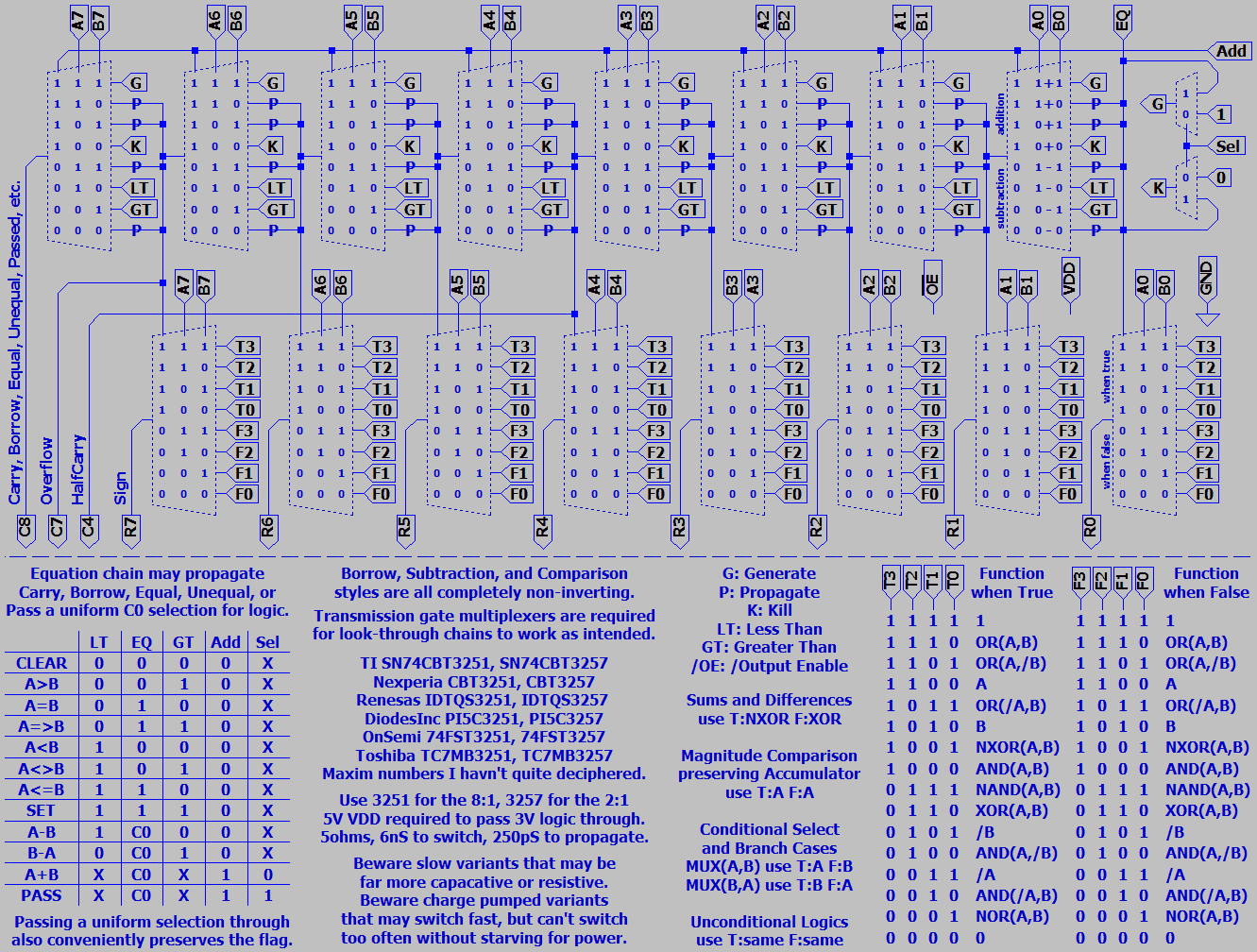

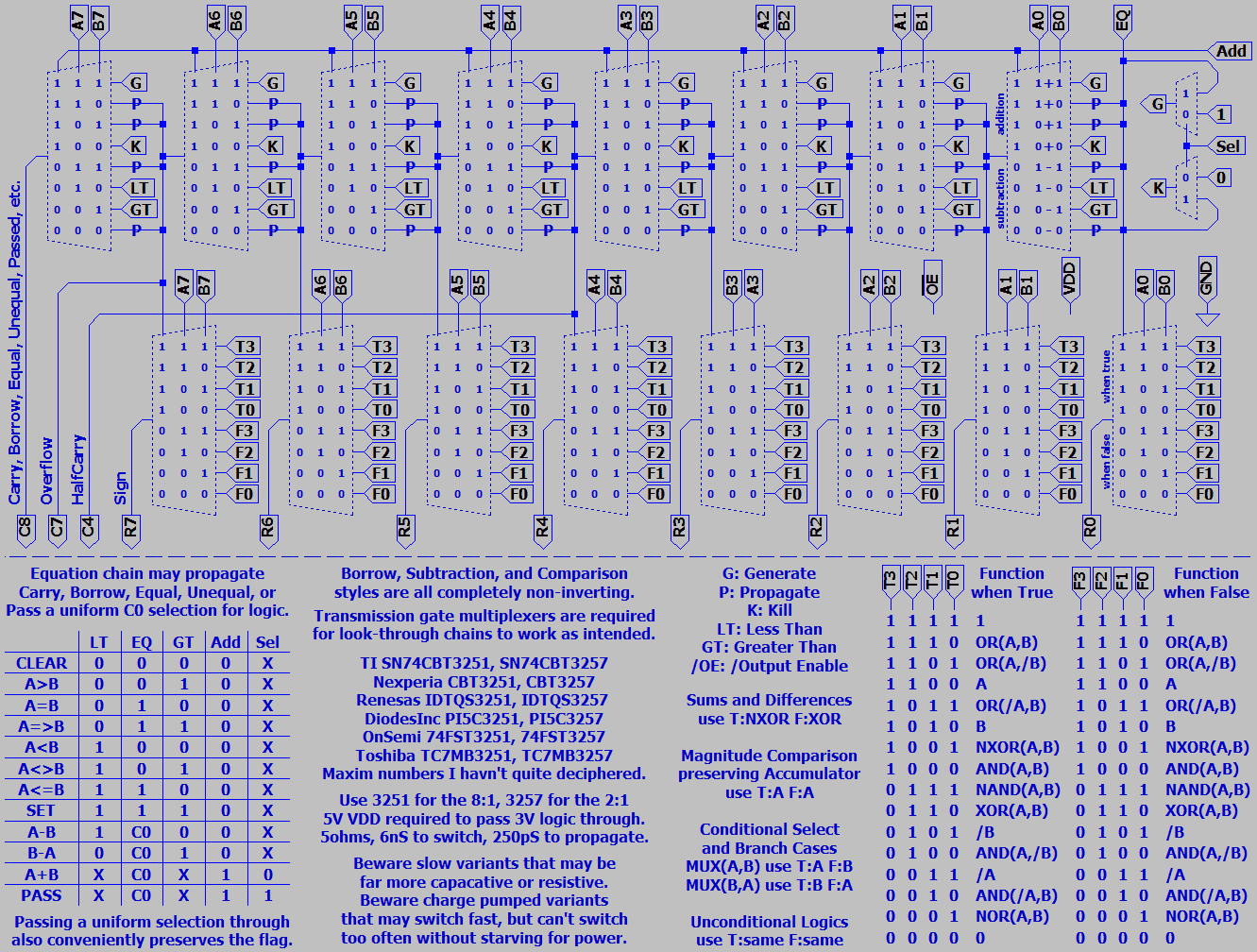

What it might look like if we chain 8 bits together for a full result...

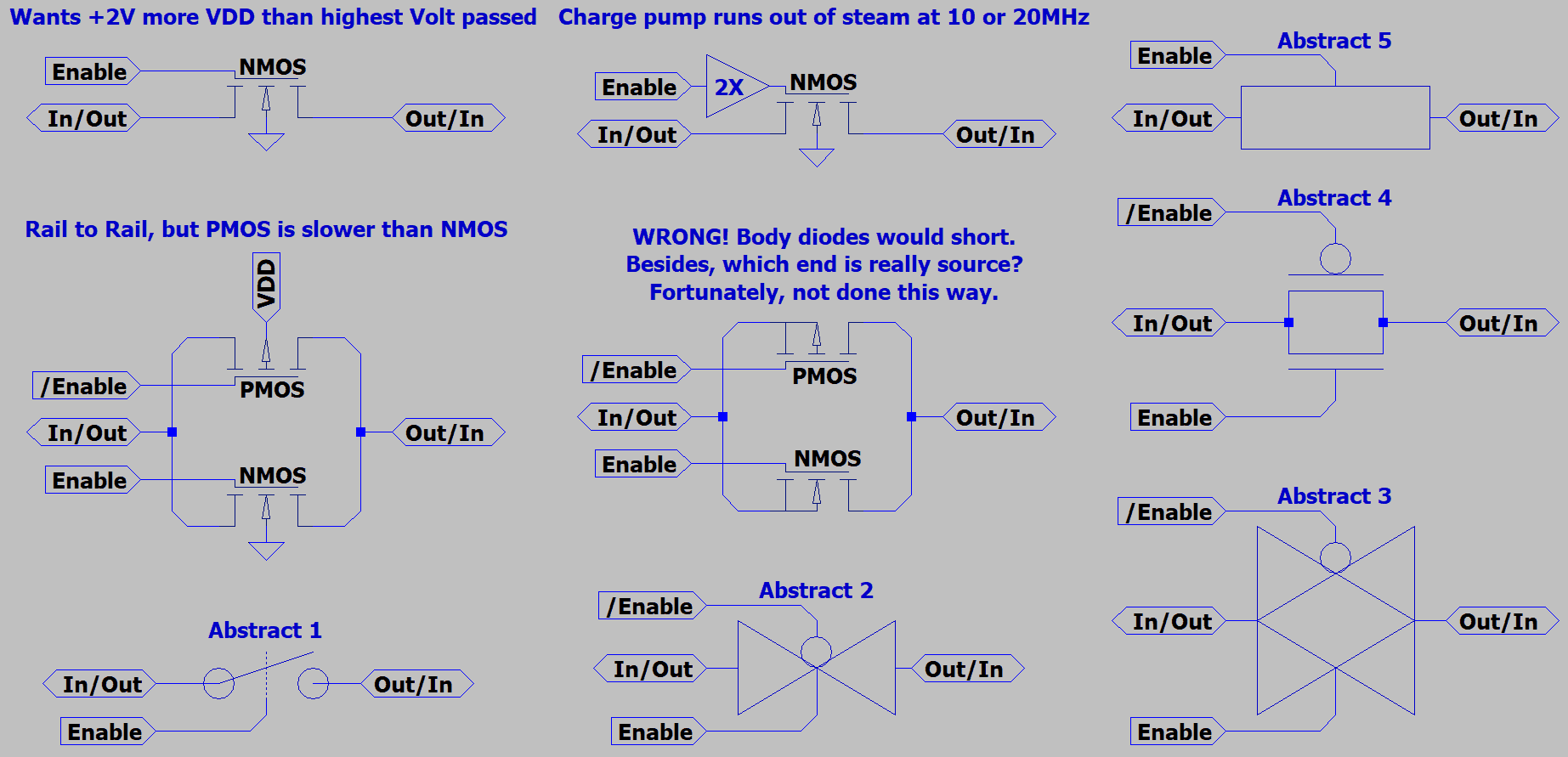

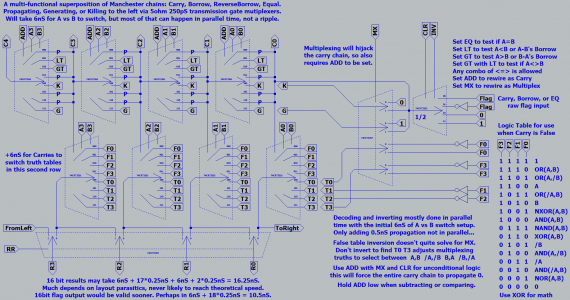

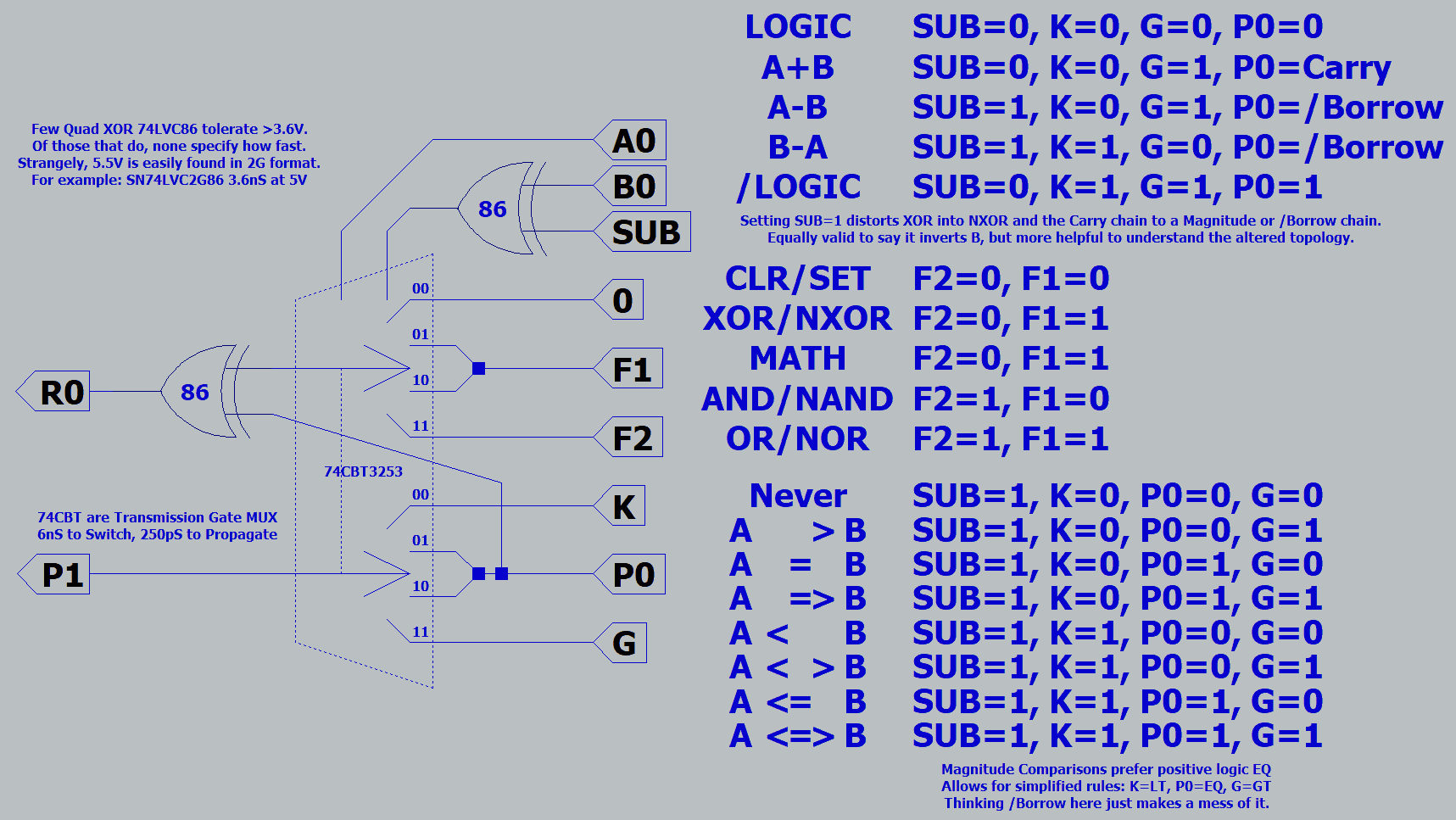

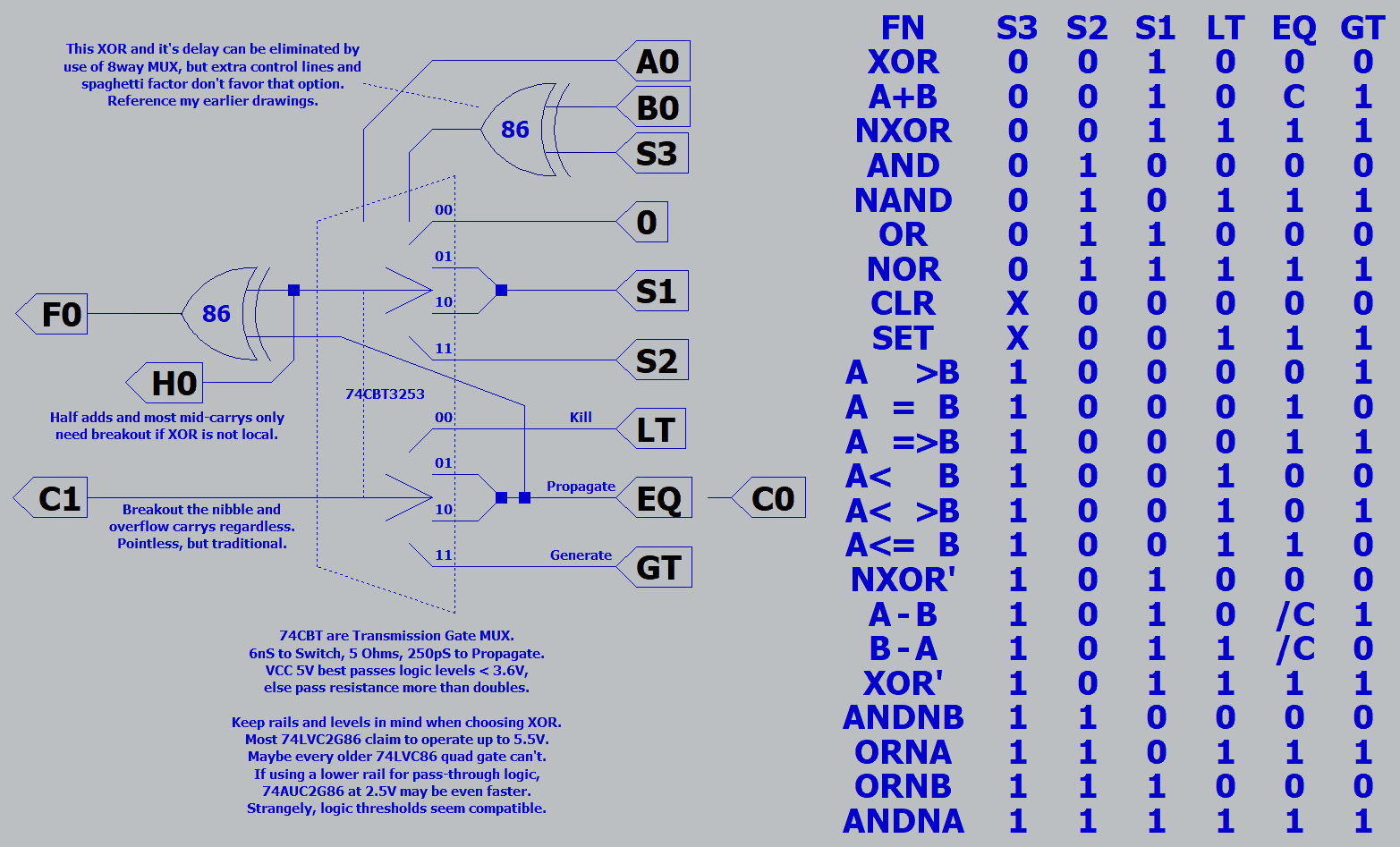

Replacing two earlier drawings in this same post that had errors.

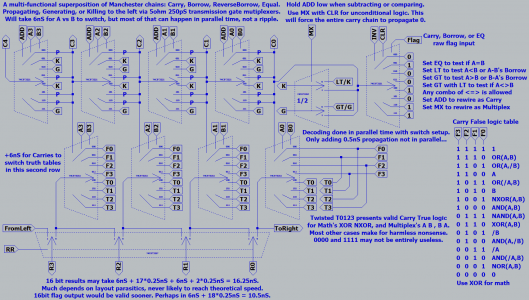

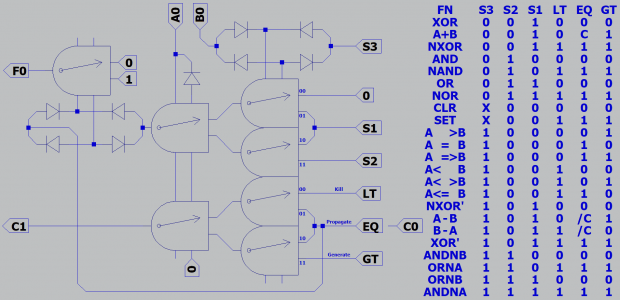

Trying here to make better sense of several earlier messes.

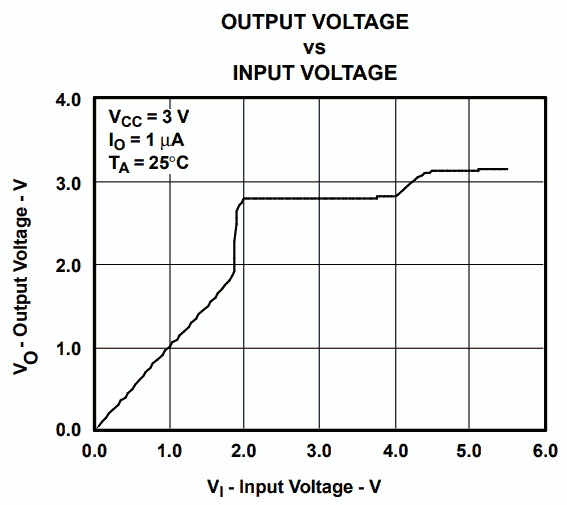

Changed "Inhibit" to "Kill" cause "I" looked too much like "1".

Changed "CarryIn" to "EQ" cause it made better sense of the new comparator functions.

"C" never made sense for Borrow, especially since I don't get there by add with inversions.

Selection of conditional logic now hijacks Carry rather than Borrow, cause it drew easier.

Four bits might fit a module of 32 pins with power and /OE, if I were to build it...

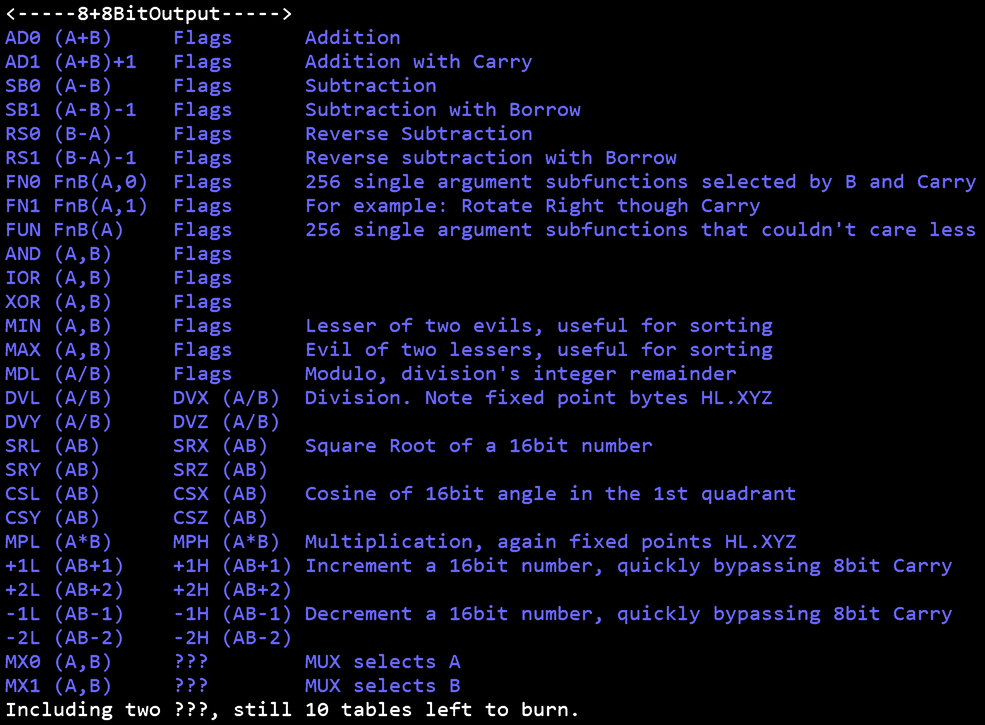

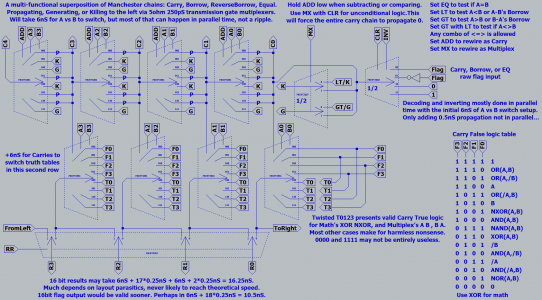

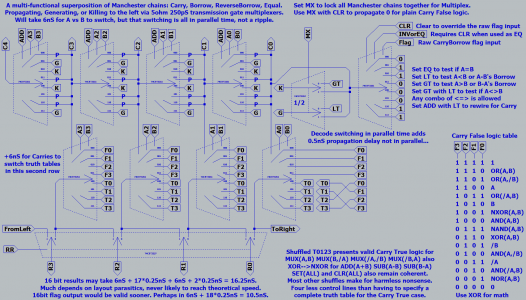

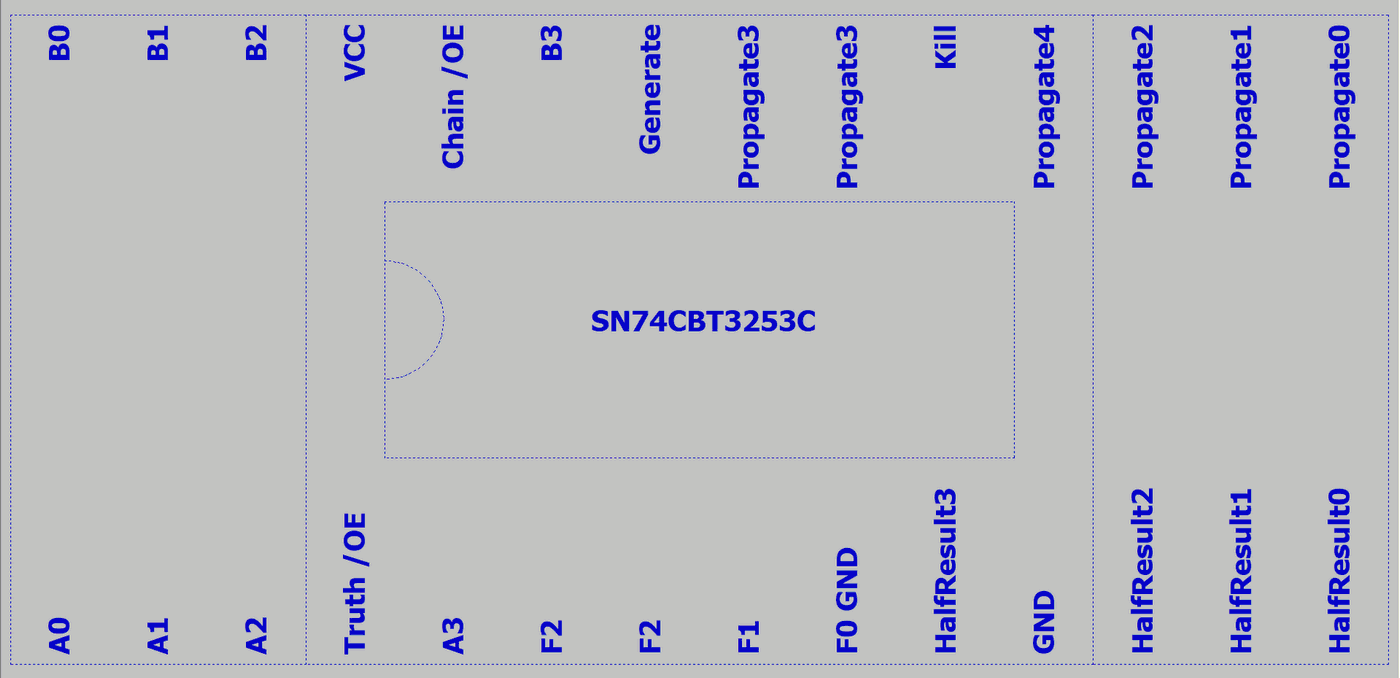

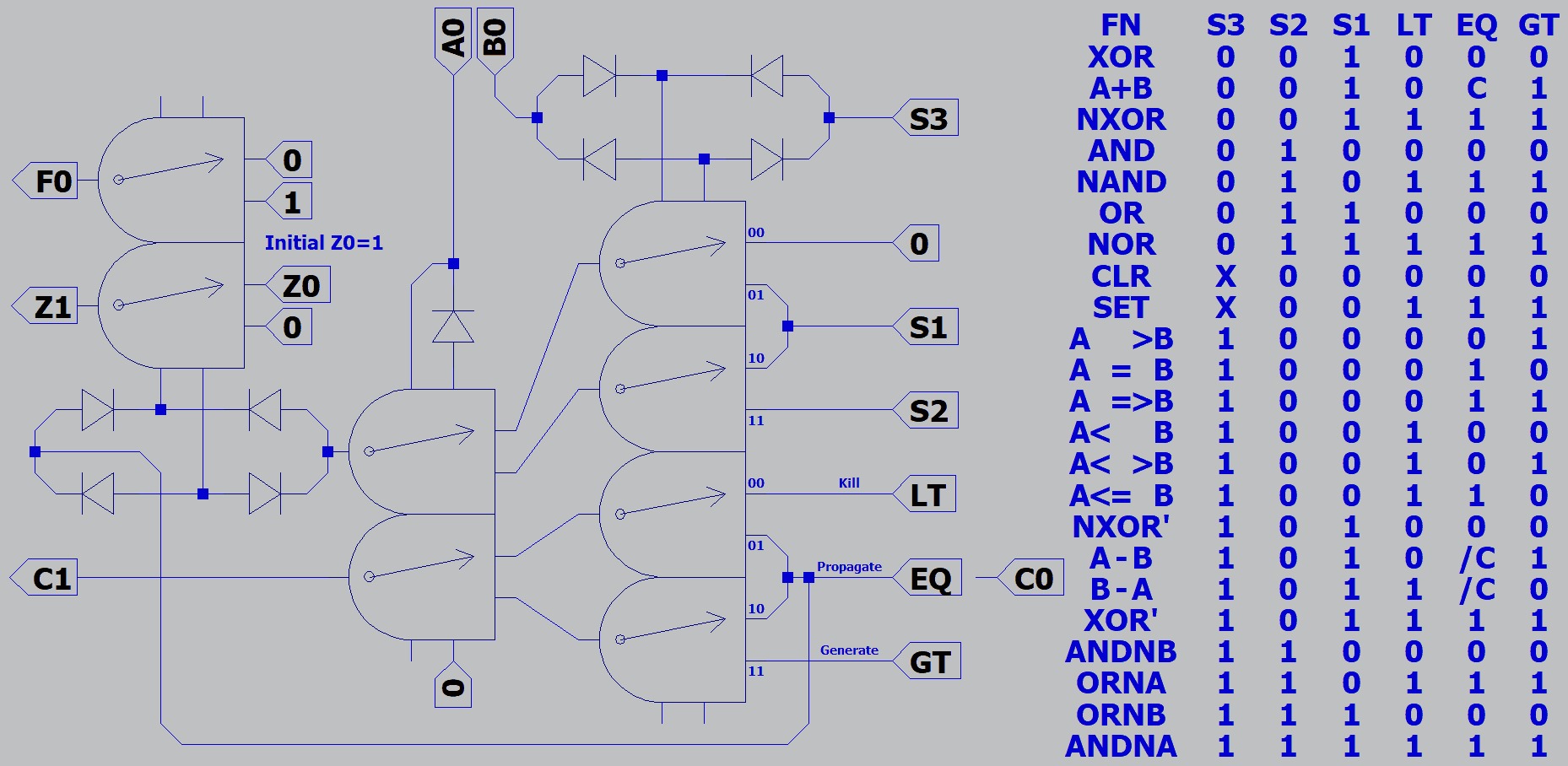

Replacing two earlier drawings in this same post that had errors.

Trying here to make better sense of several earlier messes.

Changed "Inhibit" to "Kill" cause "I" looked too much like "1".

Changed "CarryIn" to "EQ" cause it made better sense of the new comparator functions.

"C" never made sense for Borrow, especially since I don't get there by add with inversions.

Selection of conditional logic now hijacks Carry rather than Borrow, cause it drew easier.

Four bits might fit a module of 32 pins with power and /OE, if I were to build it...

Last edited:

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)