- Joined

- May 18, 1997

- Messages

- 55,634

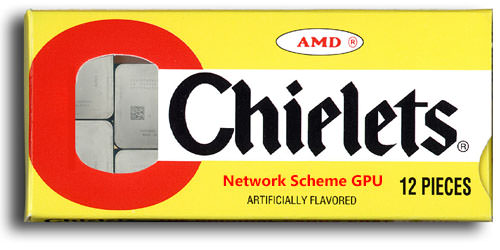

Silicon interposers are nothing new to the geeks around these parts, as we have seen AMD use these for a while now in regards to Vega GPUs and HBM2. AMD is however outlining some plans on how to use these interposers to connect full networks of CPUs and GPUs onto one piece of silicon. This is being referred to as "chiplets." And it was highly intersint that the one example showed multiple GPU chiplets in use. Thanks cageymaru.

A future system might contain a CPU chiplet and several GPUs all attached to the same piece of network-enabled silicon.

Amazingly, if you follow those rules you can pretend everything else on the interposer—all the other logic chiplets, memory, the interposer’s own network, everything—is just one node on the network. Knowing that, separate teams of engineers can design chiplets without having to worry about how the networks on other chiplets work or even how the network on the active interposer works.

A future system might contain a CPU chiplet and several GPUs all attached to the same piece of network-enabled silicon.

Amazingly, if you follow those rules you can pretend everything else on the interposer—all the other logic chiplets, memory, the interposer’s own network, everything—is just one node on the network. Knowing that, separate teams of engineers can design chiplets without having to worry about how the networks on other chiplets work or even how the network on the active interposer works.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)