N4CR

Supreme [H]ardness

- Joined

- Oct 17, 2011

- Messages

- 4,947

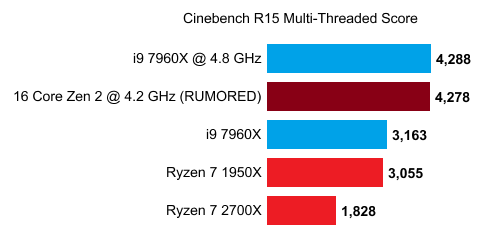

Yes but you make it out like it's a massive problem when it's not for most users here - the latency is as low or lower than intel where it counts in under 8 threads. This is the same discussion as the 16 core Zen thread but reversed.Under 8 threads means within a CCX. The latency issues I mentioned are for CCX-CCX communication within the same die or for die to die communication. if you check the TR numbers, communicating between two dies has similar latency than communicating a Xeon with other Xeon on a dual socket system!

It has more threads than most software can make use of. Let alone beyond 8 threads for some software cases and Amdahls law etc. But here, in this thread, somehow latency matters more than anything for beyond 8 threads all of a sudden?

I did look at the chart. And it clearly showed AMD has the lowest latency for a majority of desktop workloads under 8 threads, even beating the 7700k, dark blue and grey at the bottom of the latency pile. I would share your thoughts on latency regarding Zen 2 I would expect a slightly higher latency, with vastly lower latency for Chiplet>Chiplet than in existing Epyc/TR arrangements (e.g. the other half of the chart, closer to current intra-CCX latency which is top of the chart for latency. Even with a doubling they're still around a 6950X and much faster still than the ring bus 7900X latency, which no one bitches about or notices. I would also expect they have a trick to minimise this issue. IO controller is off die, don't forget that moving all that stuff off the chiplet made more room for cache - so expect more there, 32Mb L3 per chiplet if SiSoft leak isn't fudged. So it will pick up some steam in other areas than just clockspeed....did you look at the screenshot you posted (absent a link, might I add)? Now AMD is putting the memory controller off-die..?

We can't say that AMD won't be able to address the potential issues here, or how they do if they do, but it's very clear that core-to-core latency is a weakness of their technology (which your post supports) and it's something that will require scrutiney on Ryzen 3 parts with multiple CPU dies.

Screeny as much as I am not a fan of them, is from pcper.

Edit to add, Zen+ latency improved over Zen and memory speeds also can impact this, so improved MC and efficiency bump might negate most of the latency to be a wash...

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)