SomeGuy133

2[H]4U

- Joined

- Apr 12, 2015

- Messages

- 3,447

TL: DR he was patently false in his description and back tracked to save face. What he decribed was not the issue as SL correctly explained. It isn't my fault he can;t use basic words to describe something so basic. I am just ensuring bad info from lolfail9001 and Shintai doesn't spread.

He said it wasn't TIM (irrlevent) and the glue was going rogue...what the fuck ever that means.

But as he later changed his entire story after silicon lottery stated he is a mook (my word) and that its not the glue but bad application of the IHS due to insufficient pressure during the application of the IHS and crappy TIM. He than completely changed his story...original story below.

He is completely wrong in the statement i quoted. These are his words and they are patently false and inaccurate, which is why i called bullshit the entire time in this whole thread and found silicon lottery accurately and correctly explaining it, which is completely opposite of what he said below.

Don't care what you say you were completely off so just admit it.....your words are below and it is complete bullshit.

^^^^^

ummmm no? You said this....did you forget?

I see and hear back tracking.......The TIM is irrelivent!!!! Well yes or no but yes or no but yes or i don't know!?!?!?!

He even says this stupid shit. SL flatout stated its due to not putting enough pressure to push the IHS on to the die and not the glue since SL uses basically the same glue with 0 issues.

on a side note you can delid soldered chips now....not sure why you would. I didnt look too deeply at this yet but thought i would post it.

https://www.overclock3d.net/news/cp...elids_intel_s_core_i7-6950x_broadwell-e_cpu/1

this works on older gens too i guess.

interesting so Intel uses the Indium corp Indium solar preform (assuming he is correct). I was talking to someone on overclock.net about trying Nanofoil on a TEC air/waterblock build. I assume thats not what he is referring to due to this reaching 1500C during application

so silicon lottery is correct that its the application not the glue....he claimed the glue was the issue, which is not accurate.He is right.

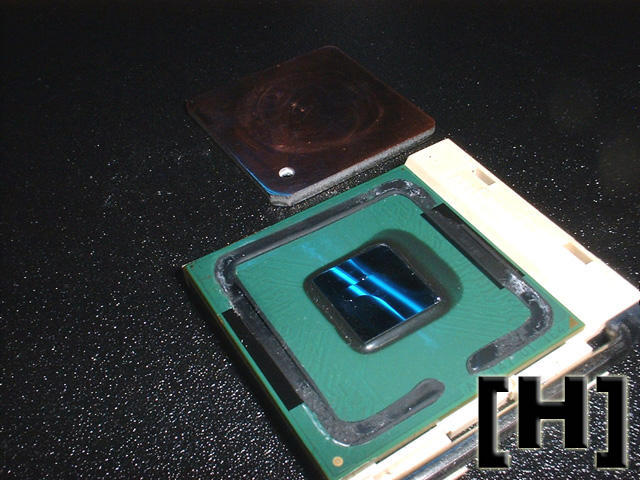

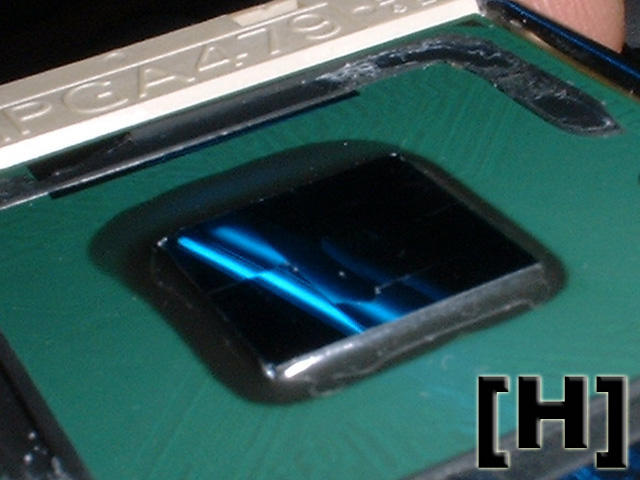

The major issue is how high the lid is raised off the core, meaning more TIM is needed to fill the gap.

ie the lid is glued in place with a large gap filled with paste.

He said it wasn't TIM (irrlevent) and the glue was going rogue...what the fuck ever that means.

But as he later changed his entire story after silicon lottery stated he is a mook (my word) and that its not the glue but bad application of the IHS due to insufficient pressure during the application of the IHS and crappy TIM. He than completely changed his story...original story below.

He is completely wrong in the statement i quoted. These are his words and they are patently false and inaccurate, which is why i called bullshit the entire time in this whole thread and found silicon lottery accurately and correctly explaining it, which is completely opposite of what he said below.

Don't care what you say you were completely off so just admit it.....your words are below and it is complete bullshit.

.........Also, it was explained thousand times already that it is not TIM at fault, TIM is irrelevant in fact, it is glue going rogue that causes temps.

^^^^^

ummmm no? You said this....did you forget?

Reasonable enough.

Oh, it is. It is not the glue material, and nobody ever claimed that. But glue application is just as freaking essential as any other property of glue, so you may as well consider it part of term "glue" in regards to the complex.

I'll give it that i was not clear enough, but my point was always constant.

I see and hear back tracking.......The TIM is irrelivent!!!! Well yes or no but yes or no but yes or i don't know!?!?!?!

Obviously it is not the glue material, it is the gluing quality hence the gap, for pete's sake, stop being obtuse.

And yes, obviously Intel's TIM is not as good of conductor as LM, nothing usable as TIM is.

He even says this stupid shit. SL flatout stated its due to not putting enough pressure to push the IHS on to the die and not the glue since SL uses basically the same glue with 0 issues.

Please link where it was done for cost cutting. If I remember correctly there was a podcast about it and cost wasn't part of the issue.

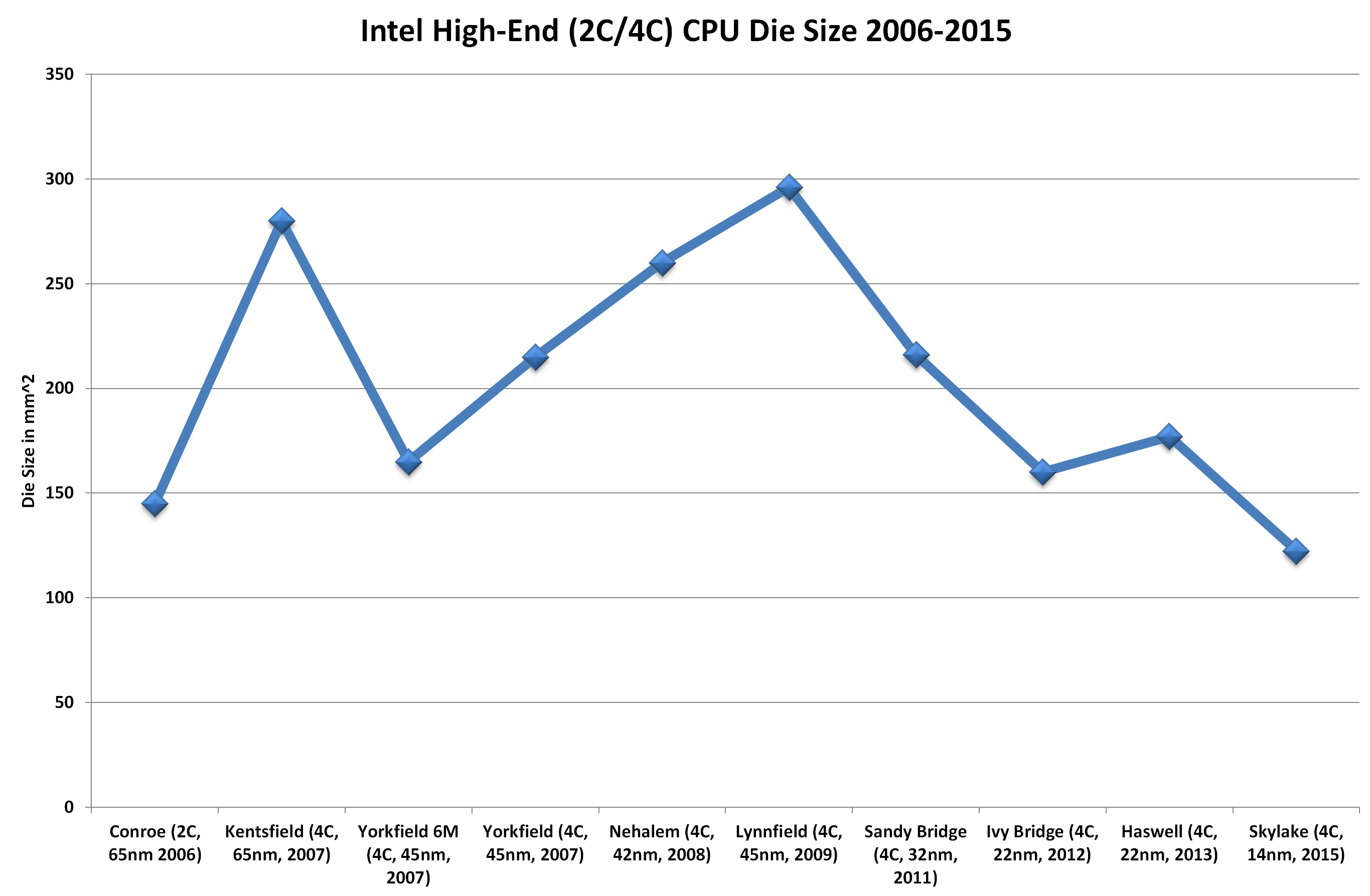

Broadwell-E up to 10 cores uses the same die at 246mm2.

http://www.overclockers.com/3step-guide-to-overclock-intel-haswell/

Speaking of temperatures, surely people will be saying “Haswell has the same problem as Ivy Bridge,” referring to the thermal paste issue. Yes, Haswell has thermal paste, but from Very Authoritative People, the TIM is not the problem. As has been posited across the net when people de-lid Ivy Bridge chips with great results, it’s really the black adhesive that’s the culprit. When you cut out that adhesive, it allows the IHS to sit closer to the CPU die, meaning there is less thermal paste through which the heat has to travel, leading to significantly lower temperatures. Intel’s TIM is really quite good, but the manufacturing process leads to that glue being just a little too thick, which is why you see such temperatures.

When you remove the adhesive you also screw the results due to moving the IHS closer to the die. Often plain on top.

on a side note you can delid soldered chips now....not sure why you would. I didnt look too deeply at this yet but thought i would post it.

https://www.overclock3d.net/news/cp...elids_intel_s_core_i7-6950x_broadwell-e_cpu/1

this works on older gens too i guess.

interesting so Intel uses the Indium corp Indium solar preform (assuming he is correct). I was talking to someone on overclock.net about trying Nanofoil on a TEC air/waterblock build. I assume thats not what he is referring to due to this reaching 1500C during application

Last edited:

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)