- Joined

- Mar 3, 2018

- Messages

- 1,713

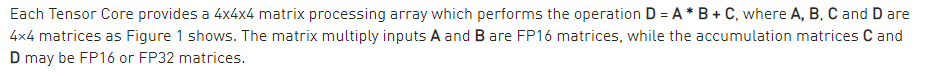

Previous roadmaps suggested that AMD would move away from the GCN architecture after Navi, but we may have just gotten a little more detail on what the next gen "Arcturus" GPU could be. KOMACHI_ENSAKA, one of the first Twitter users who spotted the allegedly leaked Gonzalo APU, just found a patent filed by AMD last month for what may be a post Navi GPU architecture. According to PCGamesN's initial analysis of the new patent, as well as an another patent that surfaced in May last year, the new GPU will move some of the resources shared within a compute unit into the individual stream processors, which the author suggests is similar to the approach used by Nvidia's more recent architectures.

With AMD’s graphics architecture already heavily compute-focused anyway, the next-gen Arcturus (maybe) design could end up being a monster on that front. And with that much complex silicon inside each stream processor in the compute unit – not a million miles away from the streaming multiprocessor (SM) design Nvidia has been using to pack out its own GPUs with – there’s the potential for not only the WinML promise of a DLSS-like feature, but genuine DXR support could also find its way into the 2020 AMD architecture. The flip-side of the more complex stream processors is that they should also represent a lower power system too. It is designed to bypass certain buffers and avoid the duplicated use of resources, and has a cache recycling system which means it doesn’t need to re-fetch data the stream processor needs to work on again.

I skimmed through the patent, and while I think I see references to things (like cache/memory operations) that AMD's individual stream processors don't normally handle, it's all way over my head.

With AMD’s graphics architecture already heavily compute-focused anyway, the next-gen Arcturus (maybe) design could end up being a monster on that front. And with that much complex silicon inside each stream processor in the compute unit – not a million miles away from the streaming multiprocessor (SM) design Nvidia has been using to pack out its own GPUs with – there’s the potential for not only the WinML promise of a DLSS-like feature, but genuine DXR support could also find its way into the 2020 AMD architecture. The flip-side of the more complex stream processors is that they should also represent a lower power system too. It is designed to bypass certain buffers and avoid the duplicated use of resources, and has a cache recycling system which means it doesn’t need to re-fetch data the stream processor needs to work on again.

I skimmed through the patent, and while I think I see references to things (like cache/memory operations) that AMD's individual stream processors don't normally handle, it's all way over my head.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)