I'm going over pipelining and stalls and forwards with MIPS architecture, and there's a couple things I'm uncertain about.

If two adjacent instructions, such as the first two of each set bellow, both use the same register, but the first isn't actually modifying that register, is there still a stall? Like if the add and first addi of the second set each modified $t0, then yea, you'd want a stall because you'd want the updated $t0 value to be used in the next instruction. But here the result of the next instruction wouldn't actually be affected since $t0 doesn't change. So is there no stall in this case? Or is there a stall just because the register is in use despite whether or not it's being written to or only read?

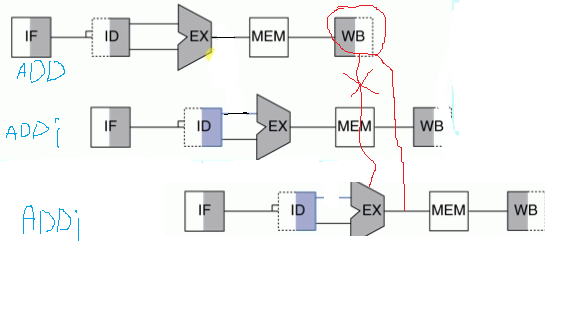

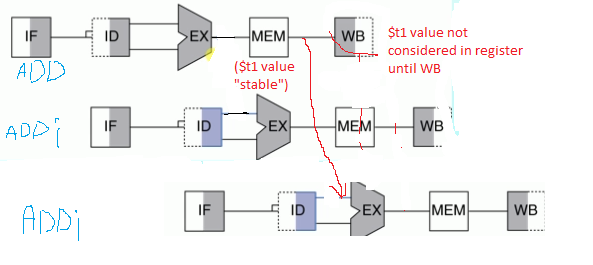

And in the first set is the first addi between the add and second addi enough of a gap not to need a stall over $t1's use? Or would you stall need forwarding to help there?

--------------------------

add $t1, $t0, $t0

addi $t2, $t0, 1

addi $t3, $t1, 1

--------------------------

addi $t1, $t0, 1

addi $t2, $t0, 2

addi $t3, $t0, 3

--------------------------

If two adjacent instructions, such as the first two of each set bellow, both use the same register, but the first isn't actually modifying that register, is there still a stall? Like if the add and first addi of the second set each modified $t0, then yea, you'd want a stall because you'd want the updated $t0 value to be used in the next instruction. But here the result of the next instruction wouldn't actually be affected since $t0 doesn't change. So is there no stall in this case? Or is there a stall just because the register is in use despite whether or not it's being written to or only read?

And in the first set is the first addi between the add and second addi enough of a gap not to need a stall over $t1's use? Or would you stall need forwarding to help there?

--------------------------

add $t1, $t0, $t0

addi $t2, $t0, 1

addi $t3, $t1, 1

--------------------------

addi $t1, $t0, 1

addi $t2, $t0, 2

addi $t3, $t0, 3

--------------------------

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)