erek

[H]F Junkie

- Joined

- Dec 19, 2005

- Messages

- 10,874

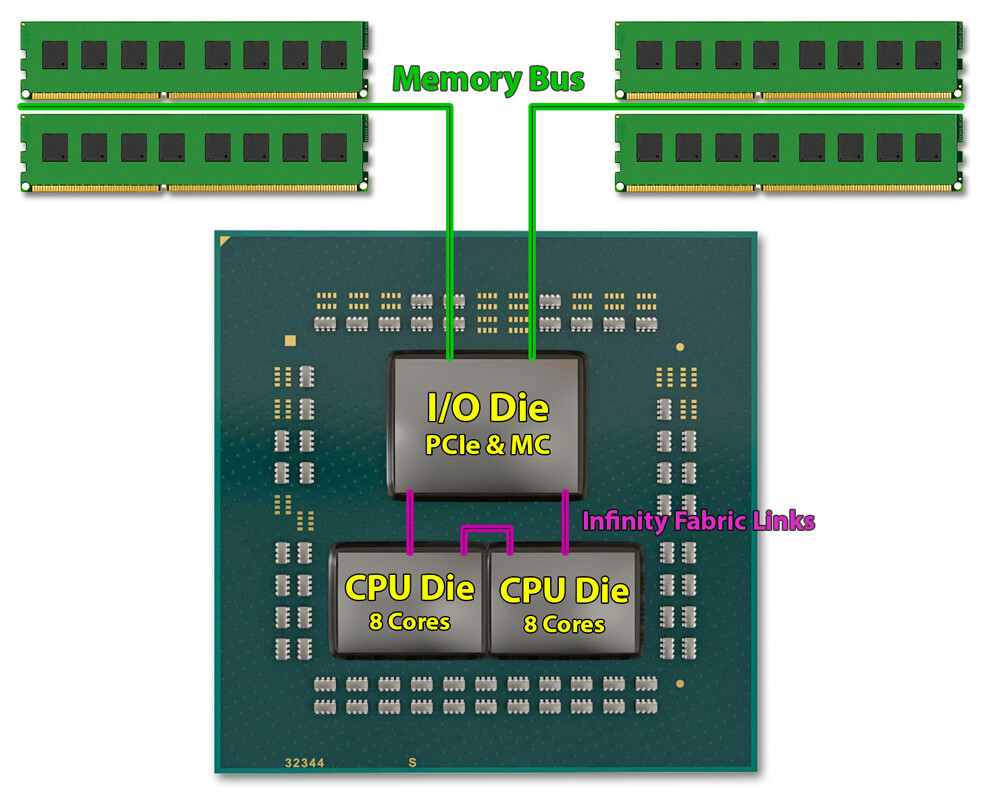

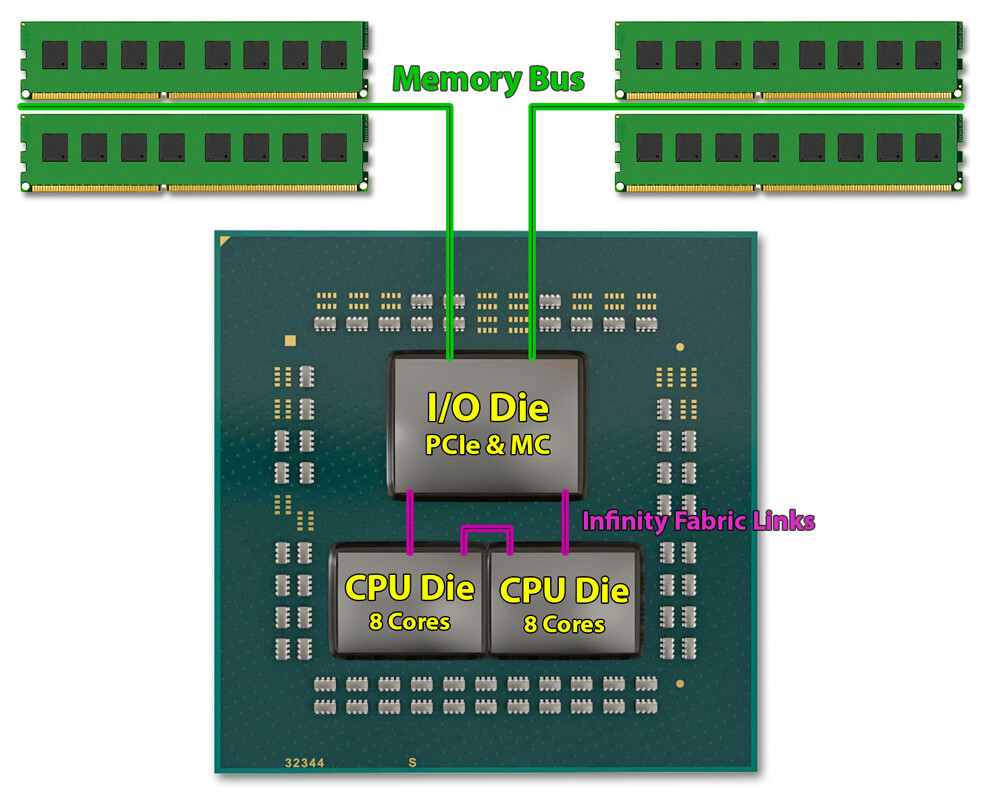

"There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9."

https://www.techpowerup.com/277053/dual-ccd-ryzen-5-5600x-and-ryzen-7-5800x-in-the-wild

https://www.techpowerup.com/277053/dual-ccd-ryzen-5-5600x-and-ryzen-7-5800x-in-the-wild

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)