erek

[H]F Junkie

- Joined

- Dec 19, 2005

- Messages

- 10,894

Seems to be a lot of interesting information and technologies in this Intel interview

"When it comes specifically to monolithic 3D, it’s entirely possible to do it. The question is going to be of thermal issues as well, so I think you know the key issue when you’re doing die stacking is that we needed to think about our architecture in terms of optimizing for the power efficient corner of where we needed to be, and we’ll gain performance on top of that from adding additional transistors, functionality, and capability with each layer. With a monolithic 3D design, we might not be able to reap that benefit if we continue with a design approach that is focusing on the optimization for the performance end of things."

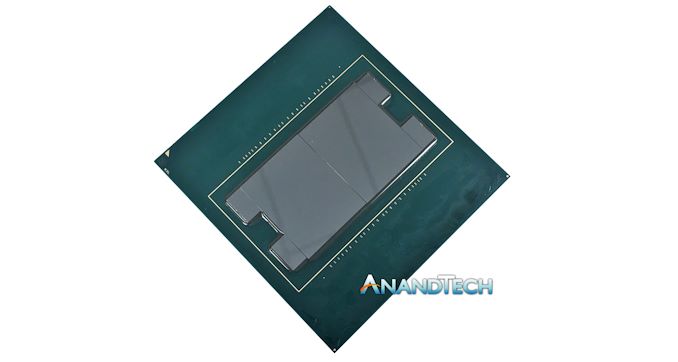

https://www.anandtech.com/show/1527...intels-ramune-nagisetty-a-future-with-foveros

"When it comes specifically to monolithic 3D, it’s entirely possible to do it. The question is going to be of thermal issues as well, so I think you know the key issue when you’re doing die stacking is that we needed to think about our architecture in terms of optimizing for the power efficient corner of where we needed to be, and we’ll gain performance on top of that from adding additional transistors, functionality, and capability with each layer. With a monolithic 3D design, we might not be able to reap that benefit if we continue with a design approach that is focusing on the optimization for the performance end of things."

https://www.anandtech.com/show/1527...intels-ramune-nagisetty-a-future-with-foveros

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)