erek

[H]F Junkie

- Joined

- Dec 19, 2005

- Messages

- 10,894

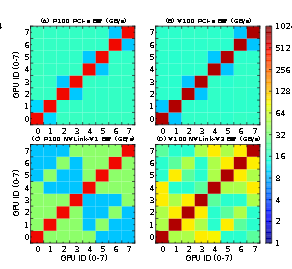

In CFR, the frame is divided into tiny square tiles, like a checkerboard. Odd-numbered tiles are rendered by one GPU, and even-numbered ones by the other. Unlike AFR (alternate frame rendering), in which each GPU's dedicated memory has a copy of all of the resources needed to render the frame, methods like CFR and SFR (split frame rendering) optimize resource allocation. CFR also purportedly offers lesser micro-stutter than AFR. 3DCenter also detailed the features and requirements of CFR. To begin with, the method is only compatible with DirectX (including DirectX 12, 11, and 10), and not OpenGL or Vulkan. For now it's "Turing" exclusive, since NVLink is required (probably its bandwidth is needed to virtualize the tile buffer). Tools like NVIDIA Profile Inspector allow you to force CFR on provided the other hardware and API requirements are met. It still has many compatibility problems, and remains practically undocumented by NVIDIA.

https://www.techpowerup.com/261357/...ased-multi-gpu-rendering-technique-called-cfr

https://www.techpowerup.com/261357/...ased-multi-gpu-rendering-technique-called-cfr

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)