About as hilarious as the lawsuit they just lost for marketing Bulldozer quad-cores as eight-core CPUs, when they were slower than Intel's quad-core CPUs?

I thought that was hilarious the entire time, after I got over AMD throwing away their good architecture and consigning themselves to irrelevance in the CPU space for a decade

Fair... although I wouldn't say Bulldozer was even that bad a design. It was actually a good design for the time... they got out fabbed by Intel no doubt. Intel had the better (ok much better) parts for awhile. AMDs FX chips where hardly terrible though

Still I'm not suggesting they market their 8 cores as 32 cores... no they need to market them exactly as what they are. Which if true would be 4 thread per core chips.

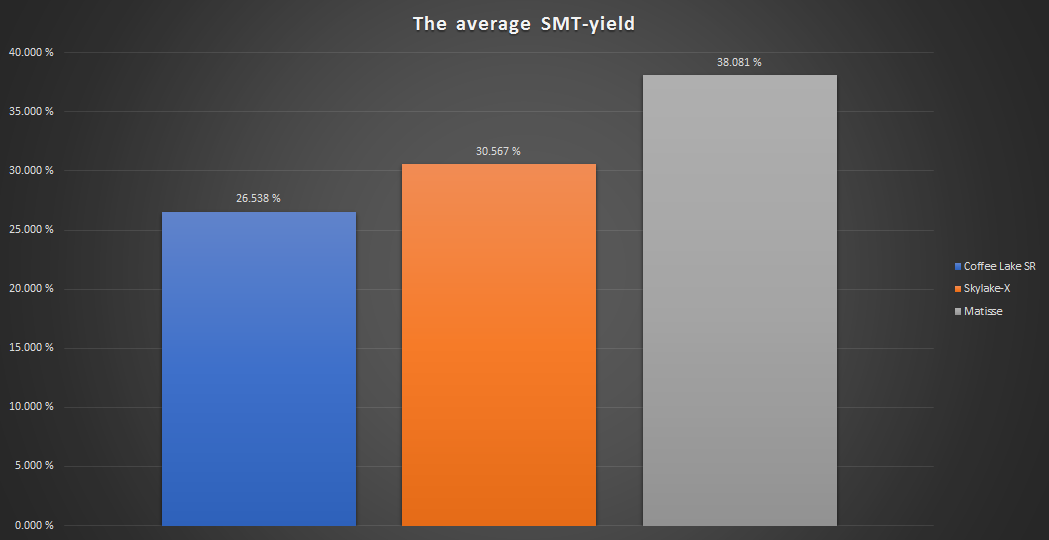

If the rumor is true I am looking forward to what Zen3 will bring to the table. AMD may have been thinking outside of the box and may push some new stuff. I don't believe SMT4 will bring a ton of real world performance... HOWEVER I could forsee some interesting implementations made possible by chiplet design. We have only really seen SMT4/8 from IBM so far and the gains there are very dependent on application. Still if AMD is able to use 7nm+ to take a 9 core chiplet as they have now and squeeze even more cache onboard in combination with an even longer prefetch history... its possible AMD might get some very nice performance gains with SMT4 even for things not traditionally effected by SMT. Games for instance mostly suck with SMT due to cache issues.... the prefetch units don't have enough history space for real time gaming loads and the split often hurts performance rather then helping. (in practice SMT is halving the amount of cache per thread, and we all know game loads are heavily influenced by cache) It is however very possible that with another doubling of cache space and 20-40% longer cache history on AMDs TAGE prefetch engine we might actually see nice FPS gains with SMT4. (I would say the advantage AMD has with SMT over Intel, and I know its not a huge advantage... is likely due to increased cache space and longer prefetch pipes as a result and little else)

Anyway I give this rumor a 50/50 of being true at best... and even if it is I would also say it could well be a 50/50 that this is a Epyc feature and the consumer Ryzens have the SMT4 unit disabled.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)