fightingfi

2[H]4U

- Joined

- Oct 9, 2008

- Messages

- 3,231

copied and pasted

PCIe 5.0 Is Ready For Prime Time

by Paul Alcorn January 17, 2019 at 6:30 AM

20 Comments

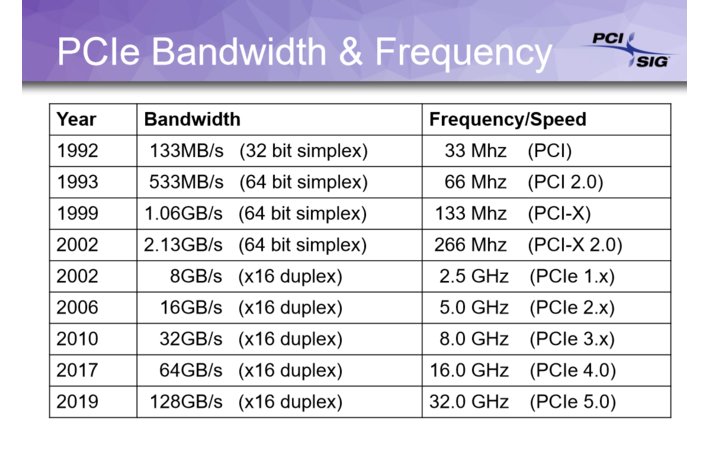

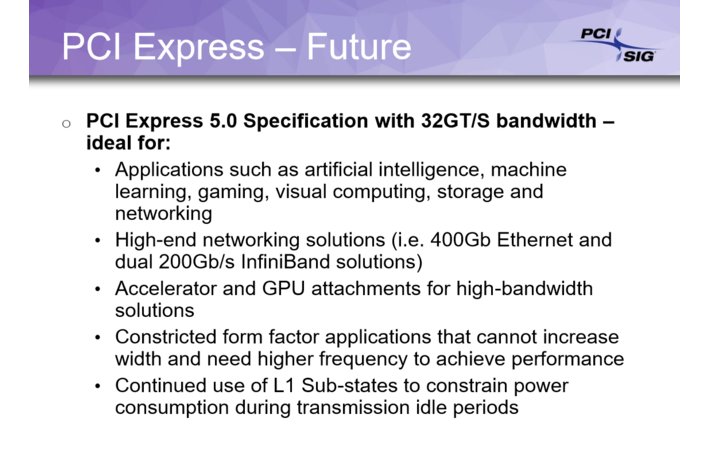

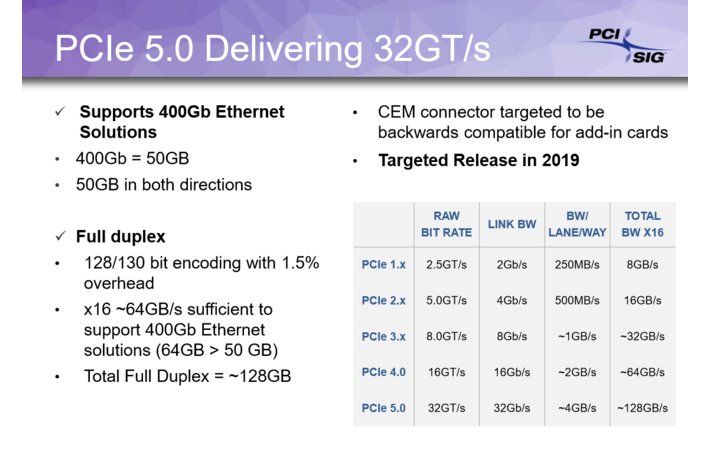

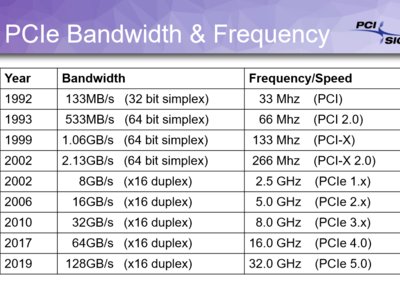

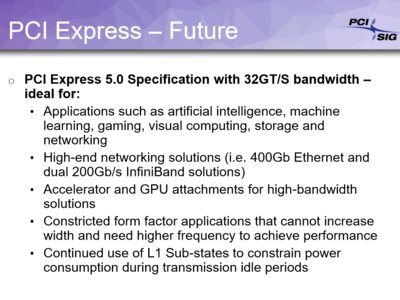

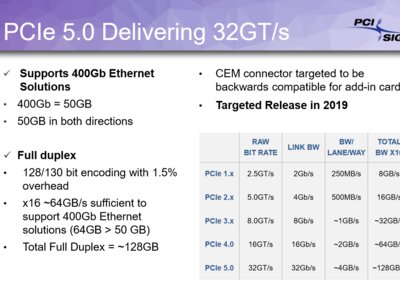

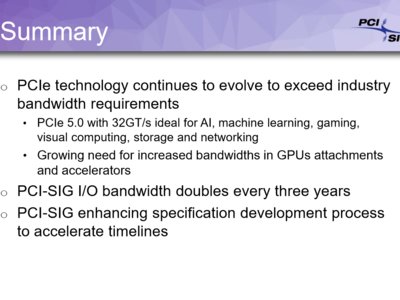

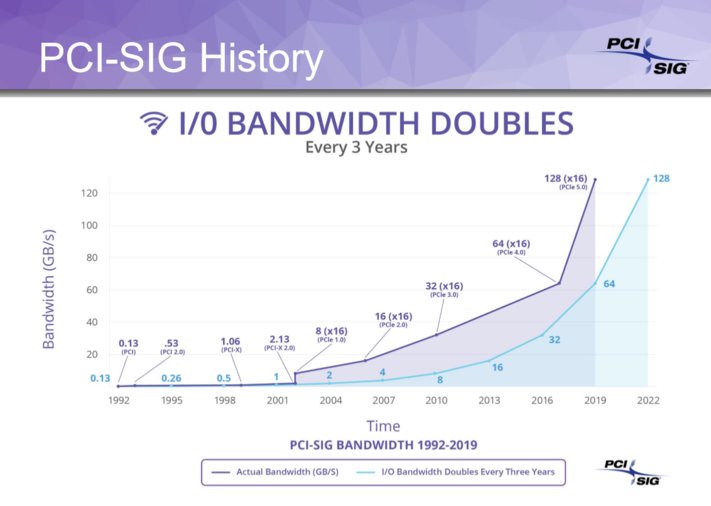

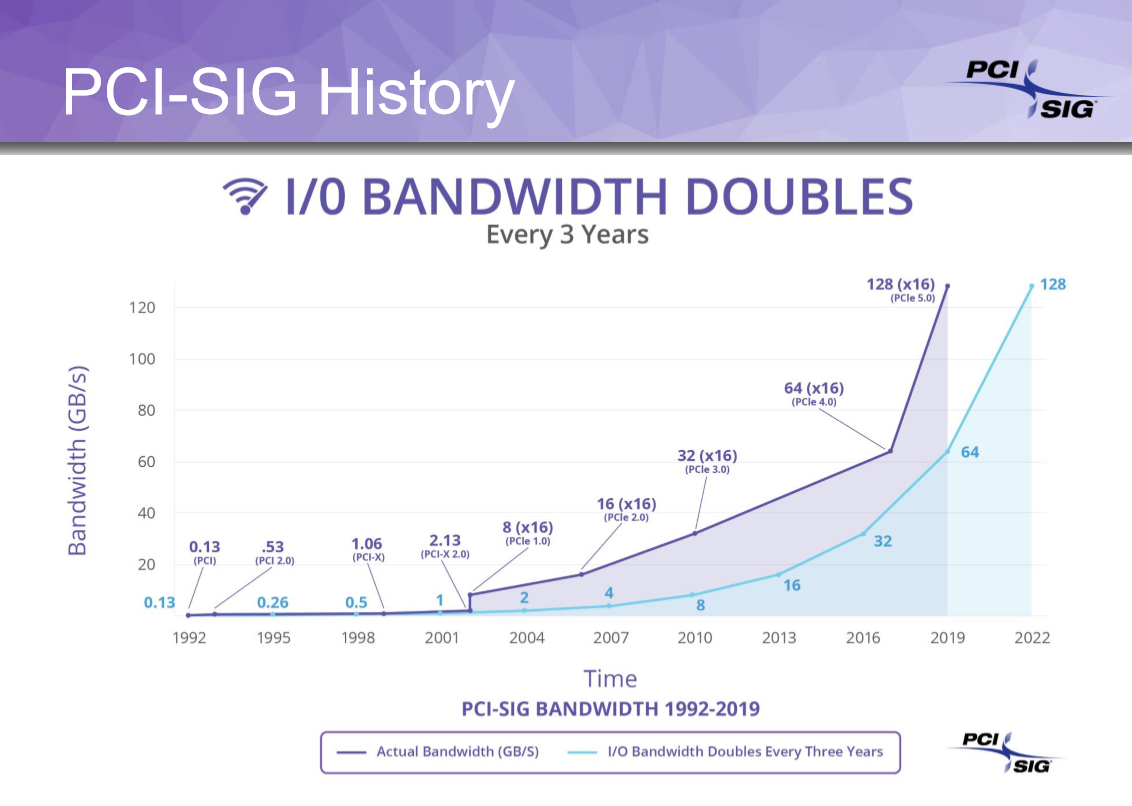

The industry has been stuck on PCIe 3.0 for roughly seven years, and even though the first support for PCIe 4.0 on the desktop will land soon in AMD's third-gen Ryzen chips and the first PCIe 4.0 SSDs just cropped up, the industry is already adopting PCIe 5.0. The new standard doubles throughput over PCIe 4.0, yielding a data rate of 32 GT/s.

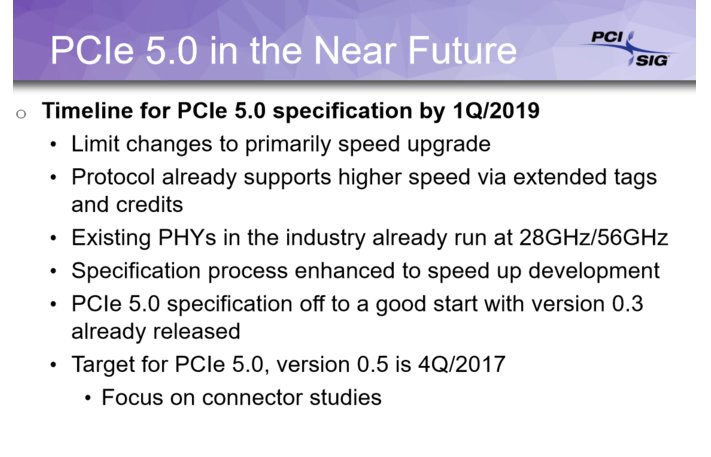

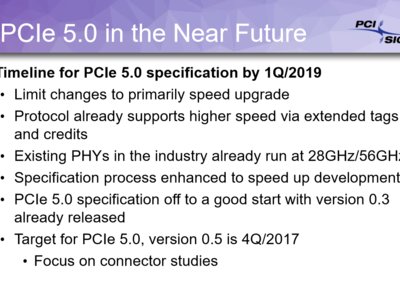

Today PCI-SIG, the organization that defines PCIe standards, announced that it ratified Version 0.9 of the PCI Express 5.0 specification, signaling that end devices will come to market in the near future. (Companies design end devices as early as revision 0.4 and often launch with 0.9.)

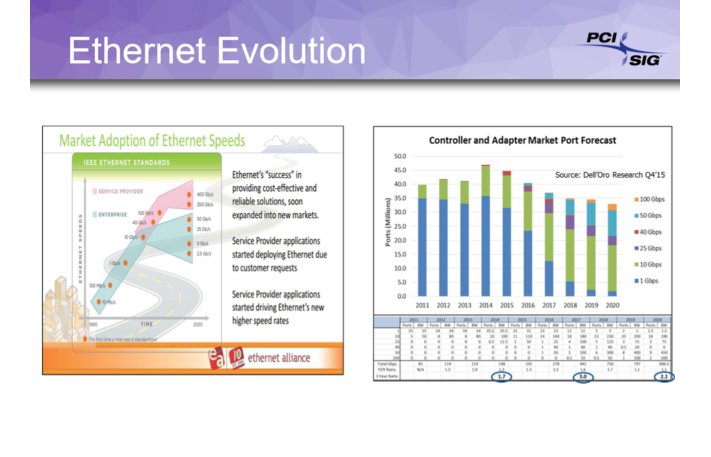

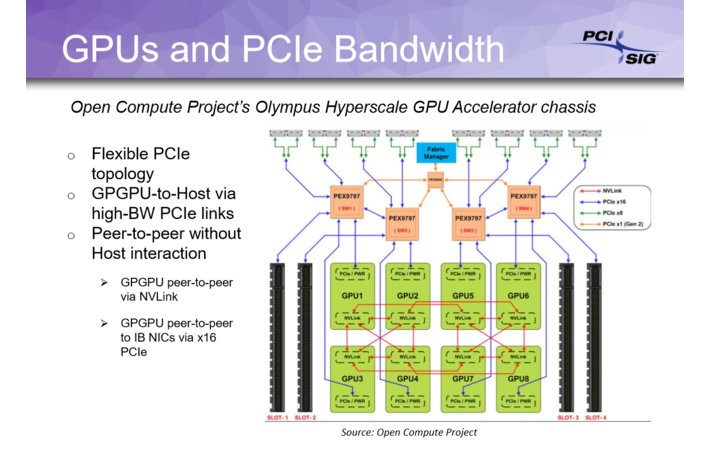

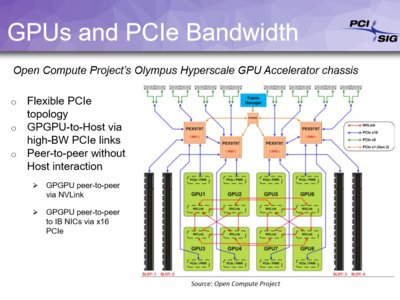

PCIe is the ubiquitous engine that pulls a big part of the computing locomotive down the track—it touches nearly every device in your computer. As such, it is the catalyst for the development of many other technologies, such as storage, networking, GPUs, chipsets, and many other devices.

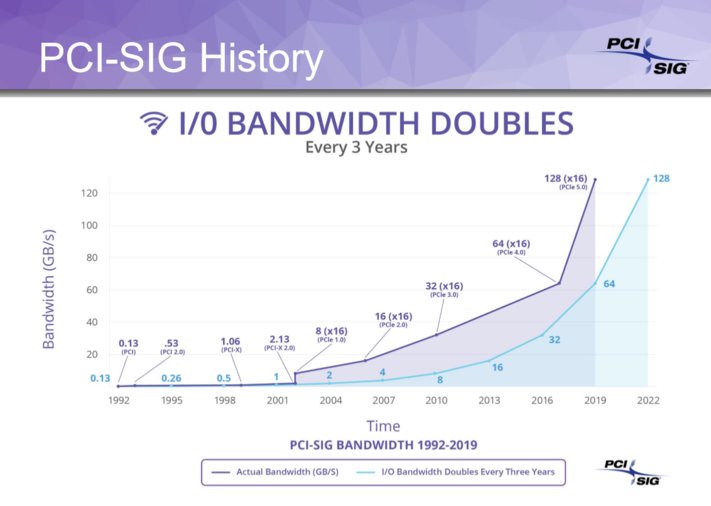

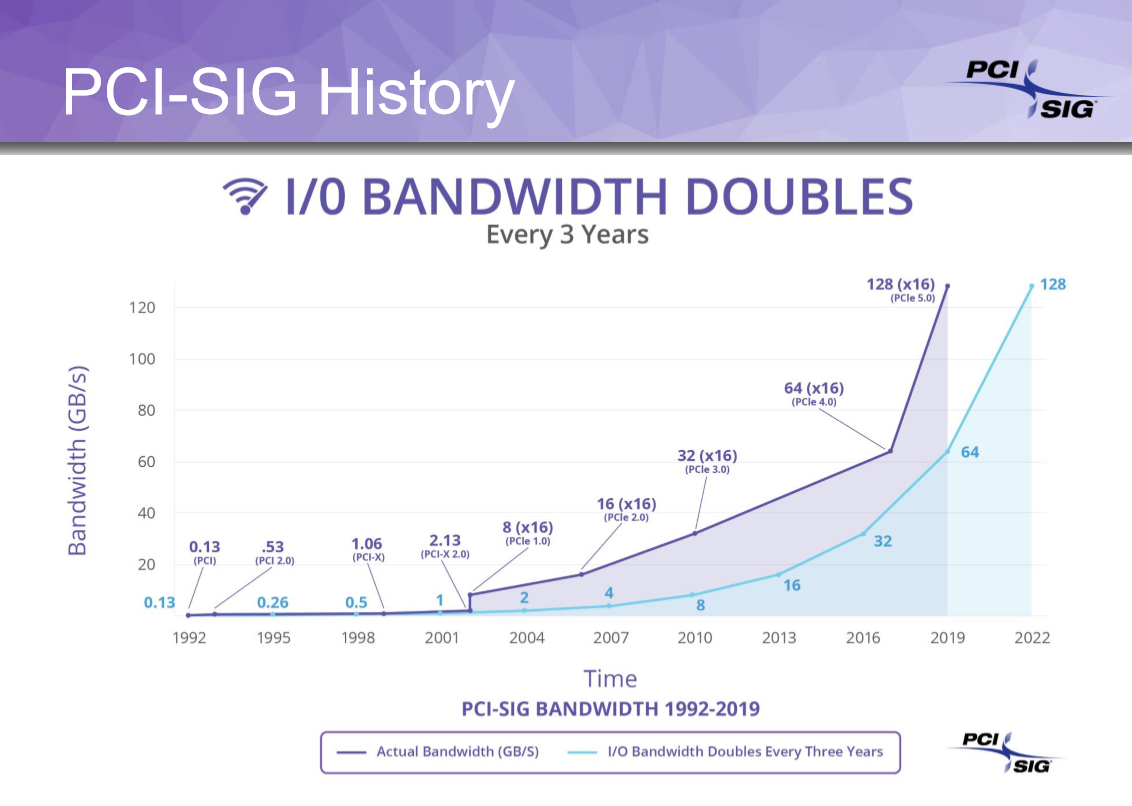

Unfortunately, the PCIe 4.0 standard was late compared to PCI-SIG's normal two-year cadence: PCIe 3.0 landed in 2010, leaving a 7-year gap between it and the introduction of PCIe 4.0. Given the faster arrival of the PCIe 4.0 standard, it's easy to assume it could be short-lived, especially given that vendors have already begun to design devices with new PCIe 5.0 PHY's.

PCI-SIG expects the two standards to co-exist in the market for some time, with PCIe 5.0 used primarily for high-performance devices that crave the ultimate in throughput, like GPUs for AI workloads, and networking applications. That means that many of the leading PCIe 5.0 devices will land in data center, networking, and HPC environments, while less-intense applications, like desktop PCs, are fine with the PCIe 4.0 interface.

PCIe 5.0 also brings other features, like electrical changes to improve signal integrity, backward-compatible CEM connectors for add-in cards, and backward compatibility with previous versions of PCIe. The PCI-SIG also designed the new standard to reduce latency and tolerate higher signal loss for long-reach applications.

The PCI-SIG defines the specification, but it has no control over when the end devices make it to market. The PCI-SIG expects to ratify the final 1.0 revision in the first quarter of 2019, and the first PCIe 5.0 devices should debut this year. Broader availability should come in 2020.

PCIe 5.0 Is Ready For Prime Time

by Paul Alcorn January 17, 2019 at 6:30 AM

20 Comments

The industry has been stuck on PCIe 3.0 for roughly seven years, and even though the first support for PCIe 4.0 on the desktop will land soon in AMD's third-gen Ryzen chips and the first PCIe 4.0 SSDs just cropped up, the industry is already adopting PCIe 5.0. The new standard doubles throughput over PCIe 4.0, yielding a data rate of 32 GT/s.

Today PCI-SIG, the organization that defines PCIe standards, announced that it ratified Version 0.9 of the PCI Express 5.0 specification, signaling that end devices will come to market in the near future. (Companies design end devices as early as revision 0.4 and often launch with 0.9.)

PCIe is the ubiquitous engine that pulls a big part of the computing locomotive down the track—it touches nearly every device in your computer. As such, it is the catalyst for the development of many other technologies, such as storage, networking, GPUs, chipsets, and many other devices.

Unfortunately, the PCIe 4.0 standard was late compared to PCI-SIG's normal two-year cadence: PCIe 3.0 landed in 2010, leaving a 7-year gap between it and the introduction of PCIe 4.0. Given the faster arrival of the PCIe 4.0 standard, it's easy to assume it could be short-lived, especially given that vendors have already begun to design devices with new PCIe 5.0 PHY's.

PCI-SIG expects the two standards to co-exist in the market for some time, with PCIe 5.0 used primarily for high-performance devices that crave the ultimate in throughput, like GPUs for AI workloads, and networking applications. That means that many of the leading PCIe 5.0 devices will land in data center, networking, and HPC environments, while less-intense applications, like desktop PCs, are fine with the PCIe 4.0 interface.

PCIe 5.0 also brings other features, like electrical changes to improve signal integrity, backward-compatible CEM connectors for add-in cards, and backward compatibility with previous versions of PCIe. The PCI-SIG also designed the new standard to reduce latency and tolerate higher signal loss for long-reach applications.

The PCI-SIG defines the specification, but it has no control over when the end devices make it to market. The PCI-SIG expects to ratify the final 1.0 revision in the first quarter of 2019, and the first PCIe 5.0 devices should debut this year. Broader availability should come in 2020.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)