- Joined

- Mar 3, 2018

- Messages

- 1,713

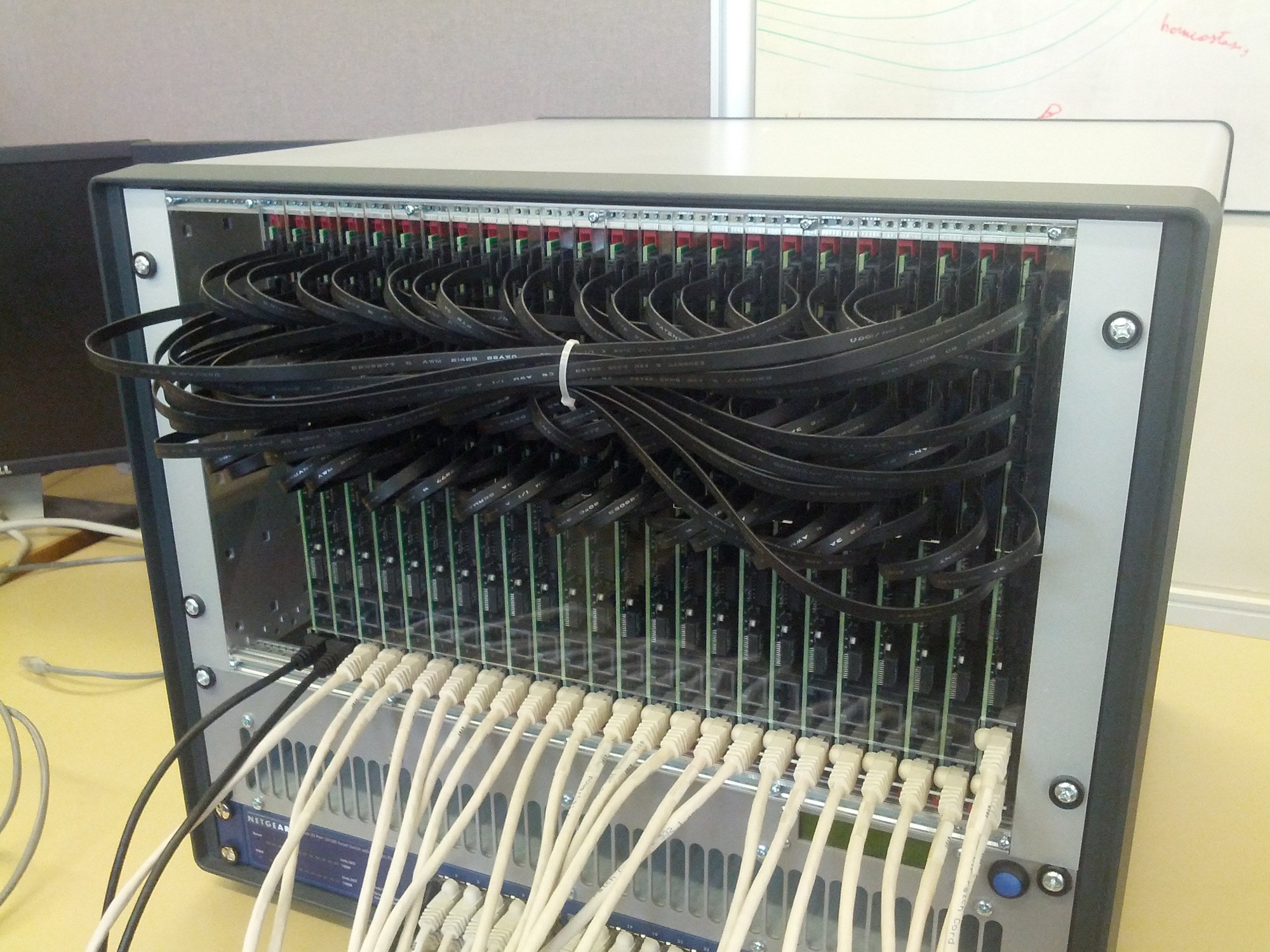

Researchers from the University of Manchester have constructed a million-core supercomputer that can allegedly "model more biological neurons in real time than any other machine on the planet." The contraption took over 10 years and many millions of dollars to construct. Unlike traditional supercomputers, the system uses a neuromorphic architecture with a special interconnect. The machine was switched on for the first time last Friday, and the creators say they've already used the architecture to simulate parts of the brain and control a robot.

Check out a video of the supercomputer here.

The SpiNNaker engine is a massively-parallel multi-core computing system. It will contain up to 1,036,800 ARM9 cores and 7Tbytes of RAM distributed throughout the system in 57K nodes, each node being a System-in-Package (SiP) containing 18 cores plus a 128Mbyte off-die SDRAM (Synchronous Dynamic Random Access Memory). Each core has associated with it 64Kbytes of data tightly-coupled memory (DTCM) and 32Kbytes of instruction tightly-coupled memory (ITCM). The cores have a variety of ways of communicating with each other and with the memory, the dominant of which is by packets. These are 5- or 9-byte (40- or 72-bit) quanta of information that are transmitted around the system under the aegis of a bespoke concurrent hardware routing system. The physical hierarchy of the system has each node containing two silicon dies - the SpiNNaker chip itself, plus the Mobile DDR (Double Data Rate) SDRAM, which is physically mounted on top of the SpiNNaker die and stitch-bonded to it. The nodes are packaged and mounted in a 48-node hexagonal array on a PCB (Printed Circuit Board), the full system requiring 1,200 such boards. In operation, the engine consumes at most 90kW of electrical power.

Check out a video of the supercomputer here.

The SpiNNaker engine is a massively-parallel multi-core computing system. It will contain up to 1,036,800 ARM9 cores and 7Tbytes of RAM distributed throughout the system in 57K nodes, each node being a System-in-Package (SiP) containing 18 cores plus a 128Mbyte off-die SDRAM (Synchronous Dynamic Random Access Memory). Each core has associated with it 64Kbytes of data tightly-coupled memory (DTCM) and 32Kbytes of instruction tightly-coupled memory (ITCM). The cores have a variety of ways of communicating with each other and with the memory, the dominant of which is by packets. These are 5- or 9-byte (40- or 72-bit) quanta of information that are transmitted around the system under the aegis of a bespoke concurrent hardware routing system. The physical hierarchy of the system has each node containing two silicon dies - the SpiNNaker chip itself, plus the Mobile DDR (Double Data Rate) SDRAM, which is physically mounted on top of the SpiNNaker die and stitch-bonded to it. The nodes are packaged and mounted in a 48-node hexagonal array on a PCB (Printed Circuit Board), the full system requiring 1,200 such boards. In operation, the engine consumes at most 90kW of electrical power.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)