cageymaru

Fully [H]

- Joined

- Apr 10, 2003

- Messages

- 22,076

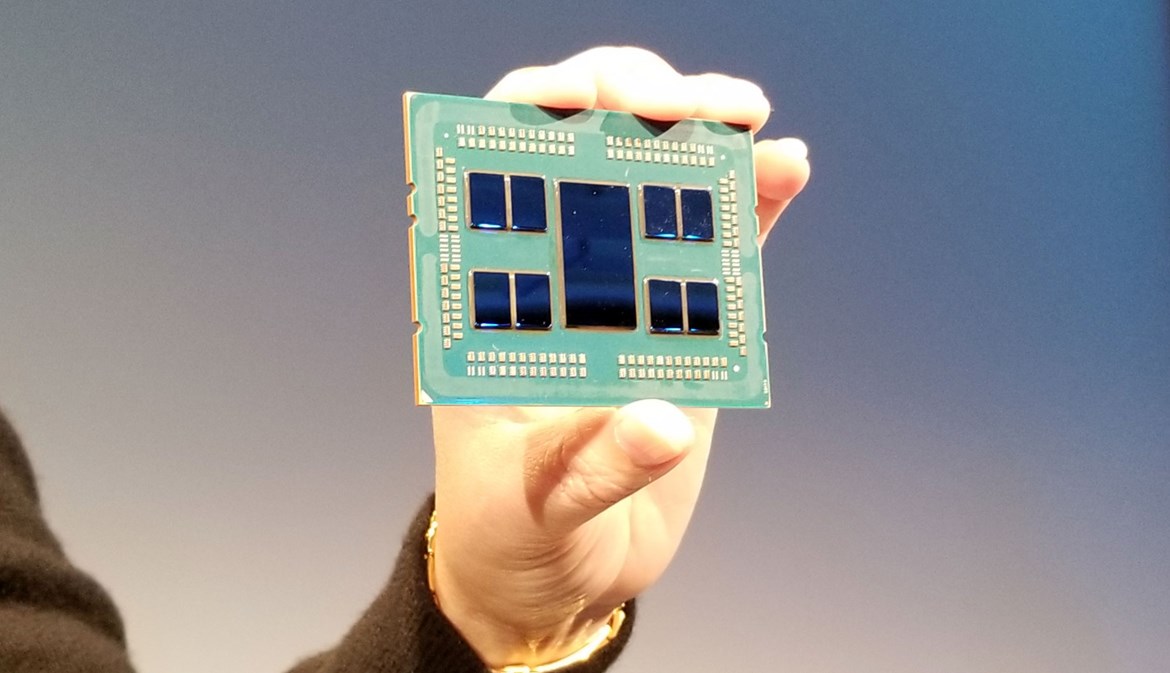

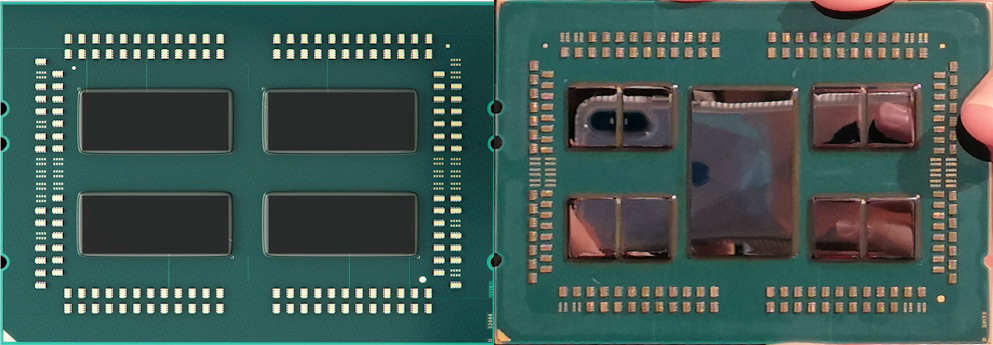

HotHardware has video of the C-Ray raytracing benchmark shown at the AMD Horizon Event. The AMD exhibit demonstrated just how powerful the new 7nm EPYC Rome architecture is with its new chiplet design that was leaked by AdoredTV. An Intel 8180M dual socket Xeon Platinum CPU server with 56 cores total and 112 threads was matched against a single AMD Zen 2 EPYC Rome 64-core CPU based server. Needless to say, the 7nm AMD EPYC Rome CPU easily won the battle. AMD CEO Dr. Lisa Su says that the 7nm EPYC Rome CPU will be a 64-core, 128-thread processor. The entire slideshow can be viewed here. Thanks juanrga !

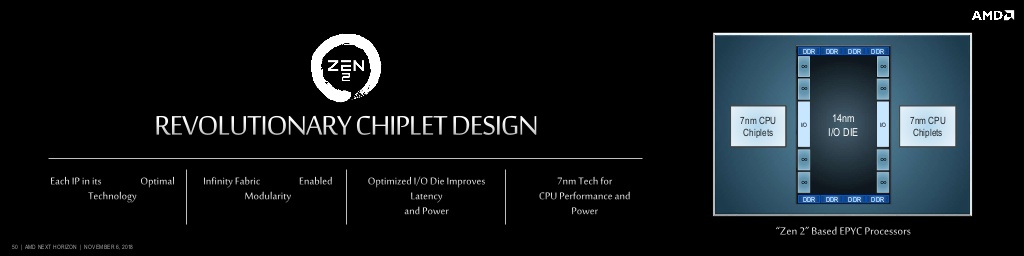

In addition, AMD has been able to add some security enhancements with Zen 2 as well, including hardware mitigation for recently discovered Spectre CPU vulnerabilities. AMD has also increased the number of encryption keys for virtualization to allow companies to support more virtual machines. Infinity Fabric is now in its second generation, and I/O per die has been optimized to improve both latency and power. While Infinity Fabric itself is being kept on a 14nm process, the accompanying chipset for Zen will be built on 7nm.

In addition, AMD has been able to add some security enhancements with Zen 2 as well, including hardware mitigation for recently discovered Spectre CPU vulnerabilities. AMD has also increased the number of encryption keys for virtualization to allow companies to support more virtual machines. Infinity Fabric is now in its second generation, and I/O per die has been optimized to improve both latency and power. While Infinity Fabric itself is being kept on a 14nm process, the accompanying chipset for Zen will be built on 7nm.

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)

I smell a new rig in the making!

I smell a new rig in the making!